F3.3: 数字逻辑电路基础

续 基本组合逻辑电路

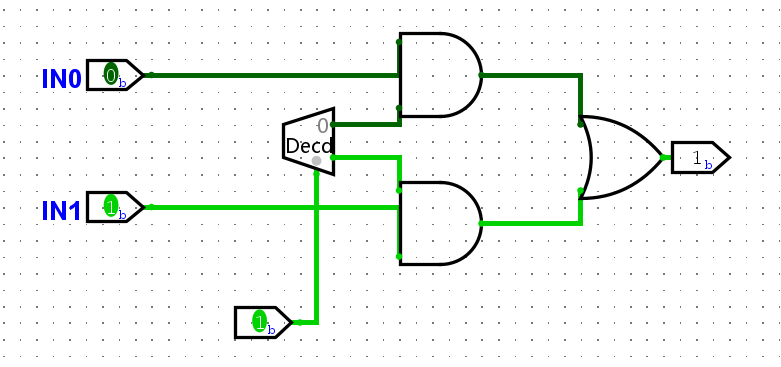

多路选择器

1.搭建一个1位2选1选择器,如图

整数的机器级表示

原码

原码是一种直观的编码,最高位表示符号位,0表示正数,1表示负数,其余位表示真值的绝对值,但这存在一个问题。

例如:

1 | 0b00000111 = 7 |

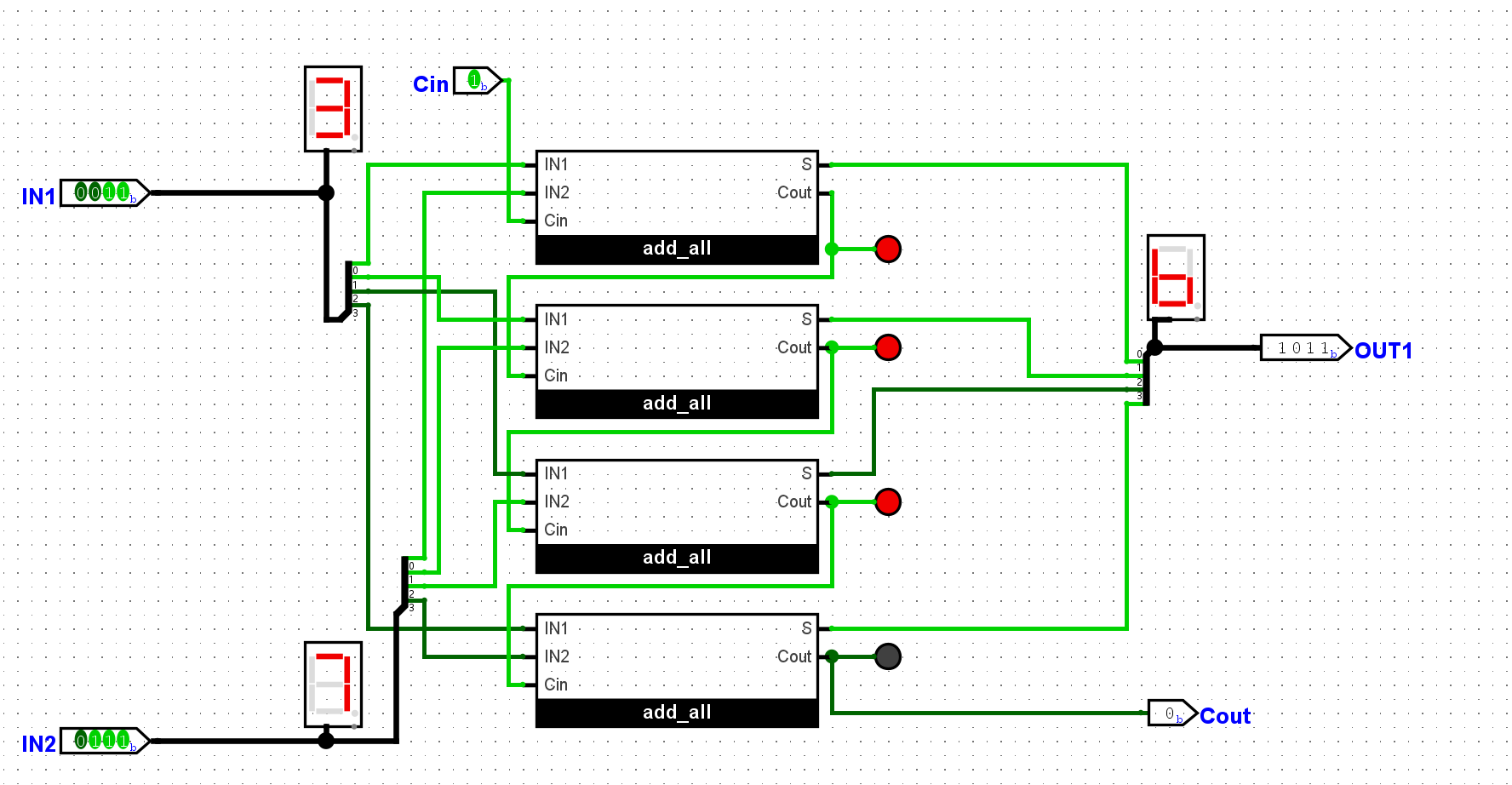

考虑采用8位的RCA进行原码加法:

1 | 0b10000111 (-7) 0b10000111 (-7) 0b00000111 (7) |

通过上述观察, 我们可以得出以下结论:

- 当两数皆为正数时, 通过RCA进行加法所得的结果按原码解释, 与将两数按原码解释后得到的结果在数学意义上相加, 两者一致. 因此, 在这种情况下, 可以直接通过RCA进行原码加法.

- 当两数为负时, RCA所得结果与数学意义不符, 区别在于符号位. 因此, 在这种情况下, 电路需要对符号位进行特殊处理.

- 当仅有一数为负时, RCA所得结果与数学意义不符, 不仅符号位有可能错误, 绝对值也错误. 因此, 在这种情况下, 不能使用RCA进行原码加法.

事实上, 在数学意义上计算第三种情况时, 应该让绝对值较大的一方减去另一方, 符号取绝对值较大的一方. 这意味着, 为了计算原码加法, 电路上还需要设计一个减法器, 然后根据两数符号和绝对值的情况, 选择出正确的处理结果.显然这种方法不具备执行的效率

反码

反码是另一种编码方式, 它尝试解决原码加法中涉及负数的问题. 具体地, 对于正数和0, 其表示与原码一致; 对于负数, 其表示为相应相反数的原码的按位取反. 例如:

补码

补码是现代计算机中常用的整数编码方式, 它进一步修复了反码计算错误时结果的偏差. 具体地, 对于正数和0, 其表示与原码一致; 对于负数, 其表示为相应相反数的原码的按位取反后加1. 例如:

0b00000111 = 7

0b11111001 = -7

0b00100010 = 34

0b11011110 = -34

溢出检测,如果按照RCA的原理的话,只用看最后输出的那个进位符就OK了,实现并没有那么的困难滴

溢出检测

Overflow = C₄ ⊕ C₃,就是看最后一位的进位和符号位的进位是否相同,如果不相同的话就有溢出,豆包给了两个例子

取:

- A=0111=+7

- B=0010=+2

逐位计算:

- 第 0 位:A0=1,B0=0,C0=0

S0=1⊕0⊕0=1

C1=(1⋅0)+(1⋅0)+(0⋅0)=0 - 第 1 位:A1=1,B1=1,C1=0

S1=1⊕1⊕0=0

C2=(1⋅1)+(1⋅0)+(1⋅0)=1 - 第 2 位:A2=1,B2=0,C2=1

S2=1⊕0⊕1=0

C3=(1⋅0)+(1⋅1)+(0⋅1)=1 - 第 3 位(符号位):A3=0,B3=0,C3=1

S3=0⊕0⊕1=1

C4=(0⋅0)+(0⋅1)+(0⋅1)=0

结果:

- 和 S=1001=−7(明显错误,7+2 应为 9,却得到 -7)

- C3=1,C4=0

- 两者不同:C4⊕C3=0⊕1=1 → 发生溢出 ✅

第二种是负数与负数的溢出

取:

- A=1001=−7

- B=1110=−2

逐位计算:

- 第 0 位:A0=1,B0=0,C0=0

S0=1⊕0⊕0=1

C1=0 - 第 1 位:A1=0,B1=1,C1=0

S1=0⊕1⊕0=1

C2=0 - 第 2 位:A2=0,B2=1,C2=0

S2=0⊕1⊕0=1

C3=0 - 第 3 位(符号位):A3=1,B3=1,C3=0

S3=1⊕1⊕0=0

C4=(1⋅1)+(1⋅0)+(1⋅0)=1

结果:

- 和 S=0111=+7(明显错误,-7 + (-2) 应为 -9,却得到 +7)

- C3=0,C4=1

- 两者不同:C4⊕C3=1⊕0=1 → 发生溢出 ✅

两个例子分别形象的展示了两个地方的进位的意义不同

机器编码就此告一段落。

时序逻辑电路

比如说电子表,新的秒数 = 旧的秒数 + 1,其输出还需要取决于其旧值。

因此, 我们需要实现一种新的电路, 它具备以下两种特性:

(1) 可以读出电路的旧状态;

(2) 可以更新电路的状态.

具备上述特性的电路称为时序逻辑电路, 它可以存储状态, 其输出由当前输入和旧状态共同决定; 相对地, 上一小节介绍的电路称为组合逻辑电路, 它们没有新旧状态的概念

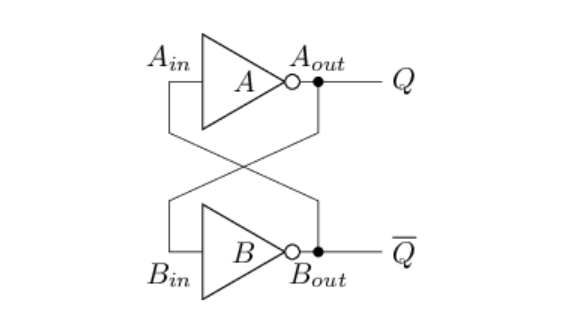

交叉配对反项器

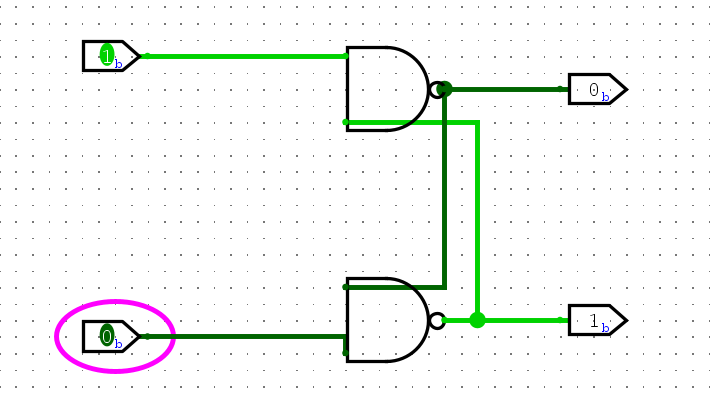

其电路结构如上图所示

假设通过线网传播到, 以及经过反相器传播到的总延迟为T, 则通过线网传播到, 以及经过反相器传播到的总延迟也为T. 上述电路的行为分4种情况讨论:

- 假设一开始, 也即. 经过时间

T后, 变为的取反, 即1, 而变为的取反, 即0. 也即, 经过时间T后, 仍有, 与时间T之前一致, 因此电路的状态保持不变. - 假设一开始, 也即. 同样分析可得, 经过时间

T后, 仍有, 与时间T之前一致, 因此电路的状态保持不变. - 假设一开始, 也即. 经过时间

T后, 变为的取反, 即1, 而变为的取反, 即1. 也即, 经过时间T后, 有, 因此电路的状态发生变化. - 假设一开始, 也即. 同样分析可得, 经过时间

T后, 有, 因此电路的状态发生变化.

但是,即便上述的交叉配对反相器处于稳定状态,我们却无法更新器状态,因为这个电路没有外部的输入,我们无法完成控制

S-R锁存器

SR锁存器(S-R Latch)通过将交叉配对反相器中的反相器换成或非门, 来向外部提供控制功能. 其中, S表示Set, 相应控制端用于对锁存器置位(设置为1); R表示Reset, 相应控制端用于对锁存器复位(设置为0). SR锁存器的逻辑符号和电路结构如下:

根据输入的不同, 我们可以分4种情况讨论SR锁存器的行为:

- 当

S=1, R=0时, 上方或非门的行为和反相器一致, 下方或非门的输出恒为0. 此时Q为1, 故将SR锁存器存储的值更新为1. - 当

S=0, R=1时, 上方或非门的输出恒为0, 下方或非门的行为和反相器一致. 此时Q为0, 故将SR锁存器存储的值更新为0. - 当

S=0, R=0时, 两个或非门的行为和反相器一致. 此时SR锁存器的行为与交叉配对反相器一致, 故SR锁存器将保持之前存储的值. - 当

S=1, R=1时, 两个或非门的输出恒为0, 此时无法表示有效的信息. 同时, 输入从S=1, R=1变为S=0, R=0时, 相当于让交叉配对反相器进入的状态. 根据上文的分析, 这将导致SR锁存器进入亚稳态, 因此需要避免.

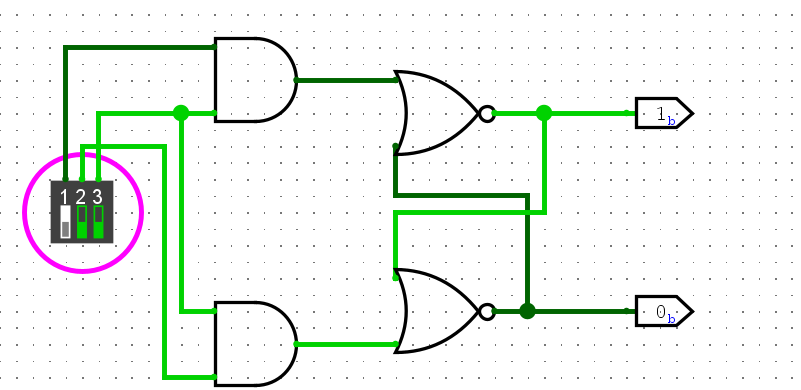

搭建SR锁存器

尝试在Logisim中通过门电路搭建一个SR锁存器. 搭建后, 通过仿真检查你的方案是否正确.

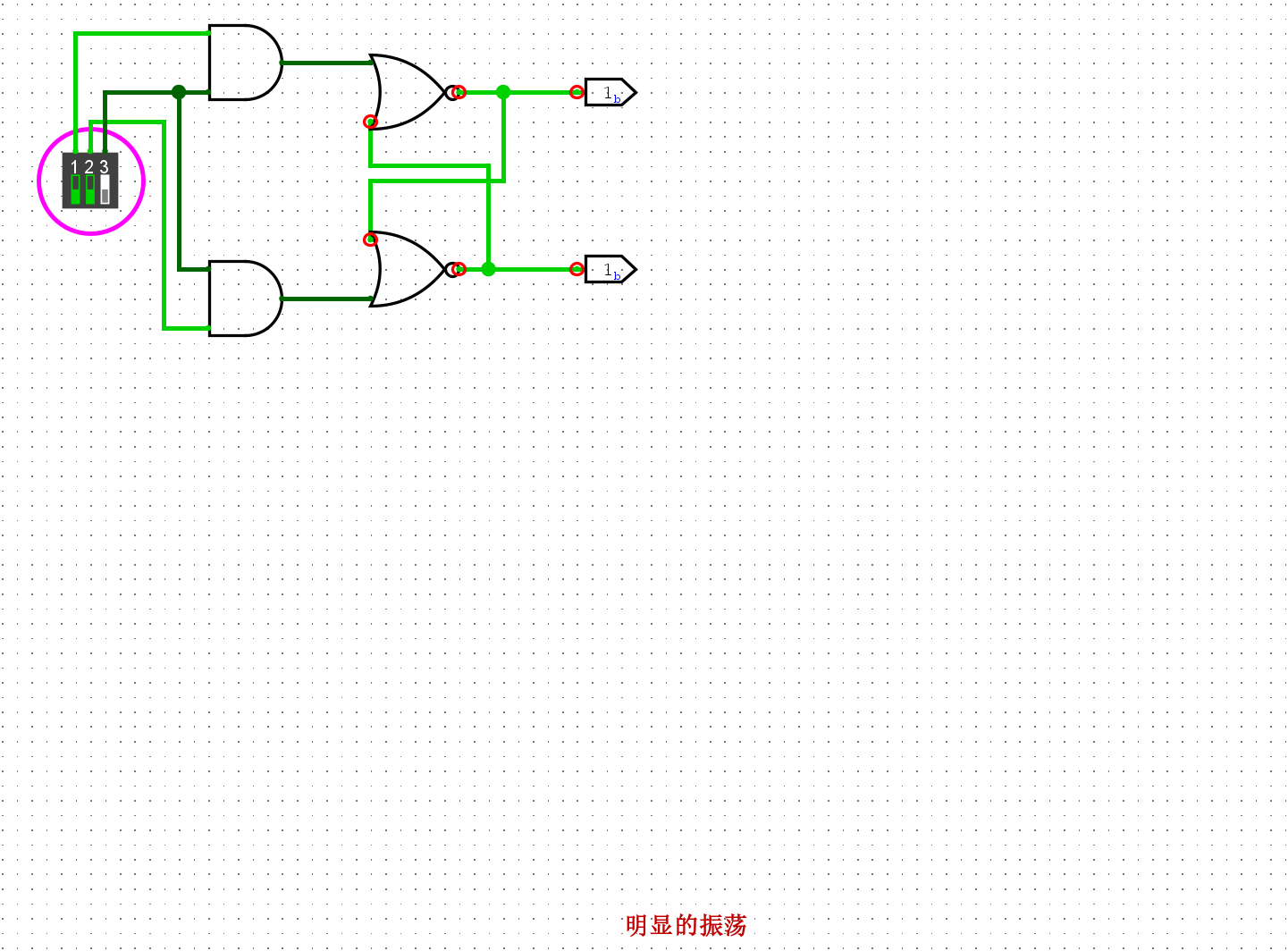

由于手工操作时, 无法通过一次点击直接将两个拨码开关从11变成00. 为了触发亚稳态, 你可以在SR锁存器前额外增加若干与门, 让另一个拨码开关同时控制这些与门的其中一个输入端, 这样就可以通过这一个拨码开关来让SR锁存器的两个输入端同时变成0了. 如果你成功触发了亚稳态, Logisim会在窗口底部显示Oscillation apparent的信息. 此时仿真将无法继续, 你需要通过Logisim的菜单重置仿真.

不负众望嘿嘿。“明显的震荡”。

这个SR锁存器,就是11到00的见光死。

其它情况就没有问题,真的很好玩!!!

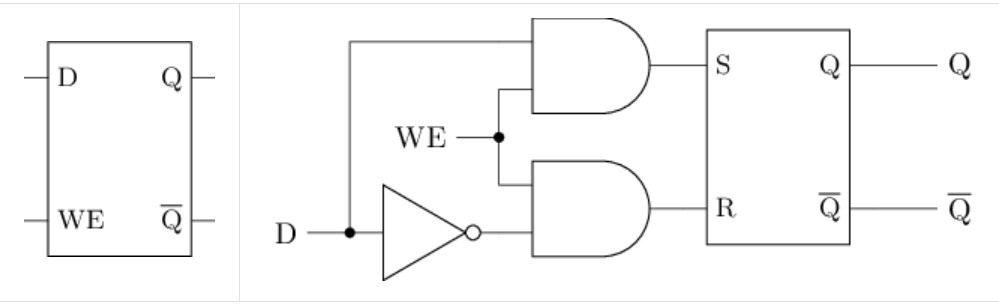

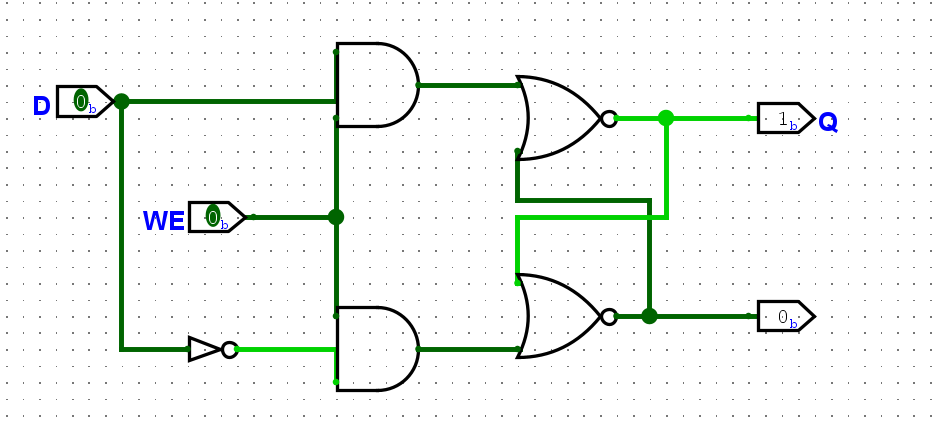

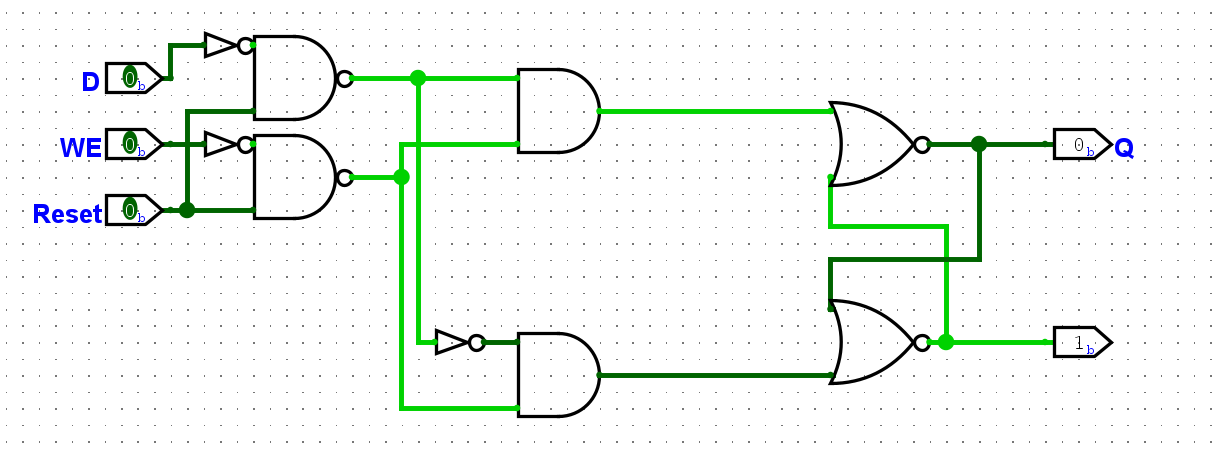

D锁存器

为了从源头避免亚稳态, 我们可以在SR锁存器前添加若干门电路, 将SR锁存器的4种输入限制成3种合法输入, 这就是D锁存器的基本思想. D锁存器的逻辑符号和电路结构如下, 其中D为输入数据, WE为写使能(Write Enable).

因为我们前置的两个与门,而且D信号一边进行了取反的操作,所以就不存在输入为11的可能了,完美的解决了上述出现的问题:所以

- WE为0时,双0输入,锁值

- WE为1时,Q值更新为D值

其实现如上图所示,接下来,我们要尝试为D锁存器添加一个用于复位的输入端和复位功能. 当复位信号有效时, D锁存器中存放的值将变为0.

与非门搭建SR锁存器

这是使用与非门实现的一个锁存器:

- 当输入为00时,值为00,违反输出相反的要求,不稳定

- 当输入为01或10时,修改寄存器值

- 当输入为11时,保存上一个时刻的锁存器值

同样的,我们也认为能够通过前置门电路的方式,将SR锁存器输入限制在三个值

搭建带复位功能的D锁存器/同步电路

我们只用在上述的基础上,在复位信号有效时,将WE设置为1,Q值更新为0即可。如果我们将其复位和使能端都接高电平,使之无效,则最终的结果相当于一个针对于输入信号的一个环形取反,输出会在0和1之间反复变化

但是, D锁存器作为存储元件, 却无法满足同步电路的要求, 即使将时钟信号连接到D锁存器的写使能端, 也仍然不满足上述要求. 如下图所示, 我们期望数据在时钟上升沿到来时写入存储元件, 且在后续时钟周期能从存储元件稳定读出该数据, 但图中红圈处违反了该特性.

这是因为锁存器属于电平触发(level-triggered)的存储元件, 只要输入发生变化, 锁存器就能立即感知, 并将该变化传播到输出端. 相比之下, 我们需要一种边沿触发(edge-triggered)的存储元件, 只有信号边沿到来时, 才将输入传播到输出端.

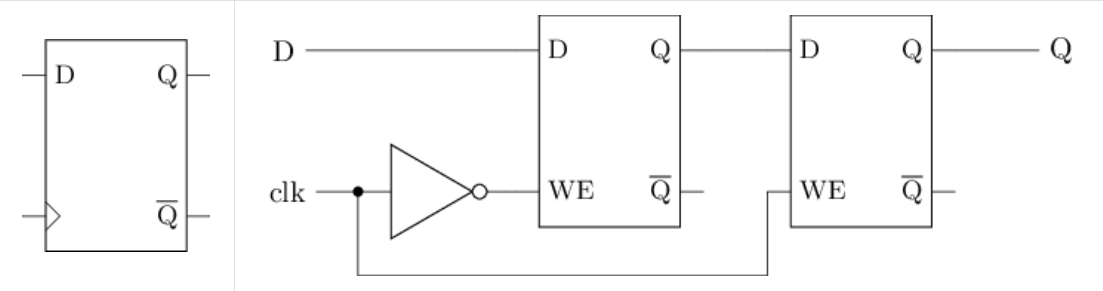

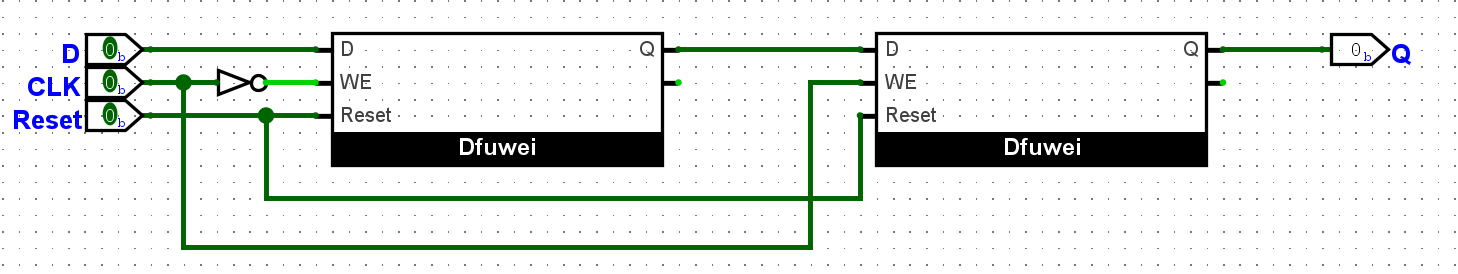

D触发器

D触发器(D Flip-Flop)是一种边沿触发的存储元件, 它基于锁存器搭建, 但可以在时钟信号维持电平的时刻巧妙地阻塞输入信号的传播. D触发器的逻辑符号如下图所示, 其中左下方的>符号表示该端口需要连接时钟信号. D触发器有多种实现方式, 这里先介绍主从式D触发器, 其结构如下图所示.

主从式D触发器由两个D锁存器构成, 左边的称为主锁存器, 右边的称为从锁存器

- 当clk为低电平时,此时主锁存器WE为高电平,数据信号可以通过主锁存器,但不能通过从锁存器,故输出端保持不变。

- 当clk的上升沿来临时,主锁存器可以抓住上升沿前的数据并且锁住,主存储器中锁住的数据将会传播到从存储器,并且作为输出

- clk维持高电平时,此时虽然从锁存器可以发生改变,但由于主锁存器未发生改变,故从锁存器的值也没有发生改变,输出端Q保持不变

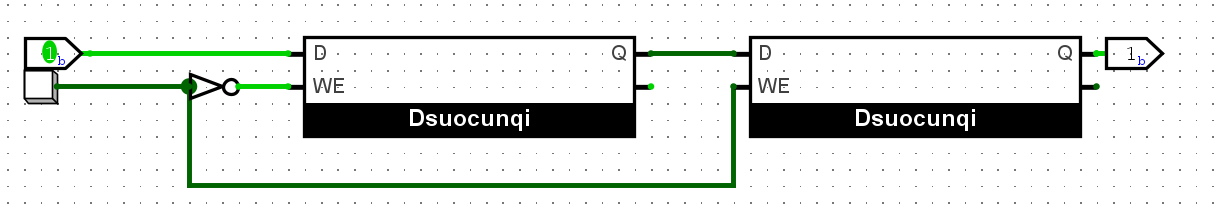

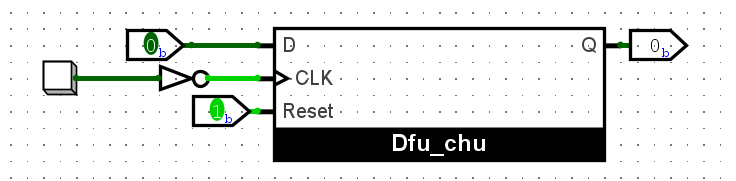

搭建D触发器

我们首先改变输入的值,然后在按下按钮的瞬间,值发生跳变。

但如果是要带复位信号的D触发器,我们可能需要一个带复位的D锁存器。我们统一使用低电实例化一个带复位功能的D触发器, 并将其输出取反后作为输入.

我们预期看到D触发器的输出将在0和1之间反复变化. 尝试和上文D锁存器的结果进行对比.平有效复位的方法。事实是这个我没有很好的进行实现,也不知道为什么,按理来说不应该呀

然后来搭建下降沿触发的D触发器,简单的想可以直接对D出发沿取一个反

就是这个样子,松开按键即完成了触发,有点意思滴

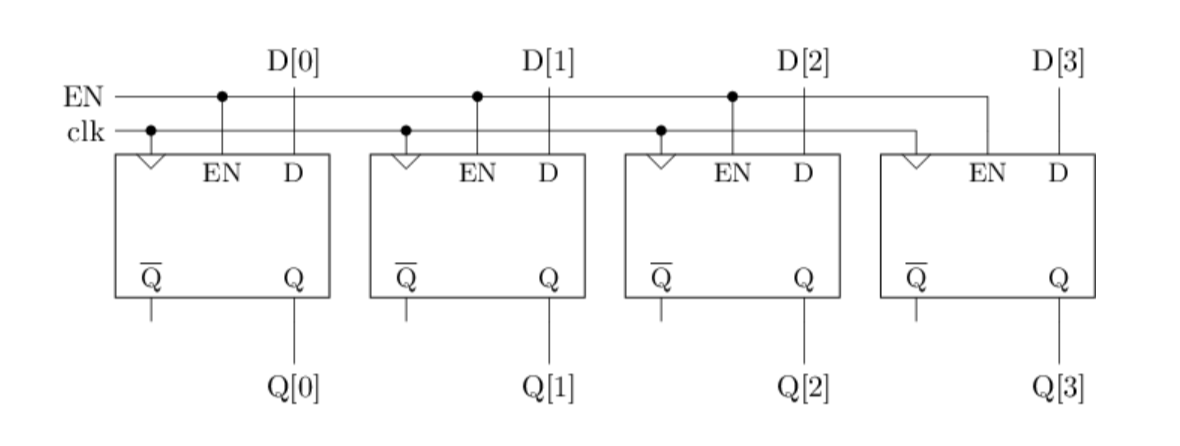

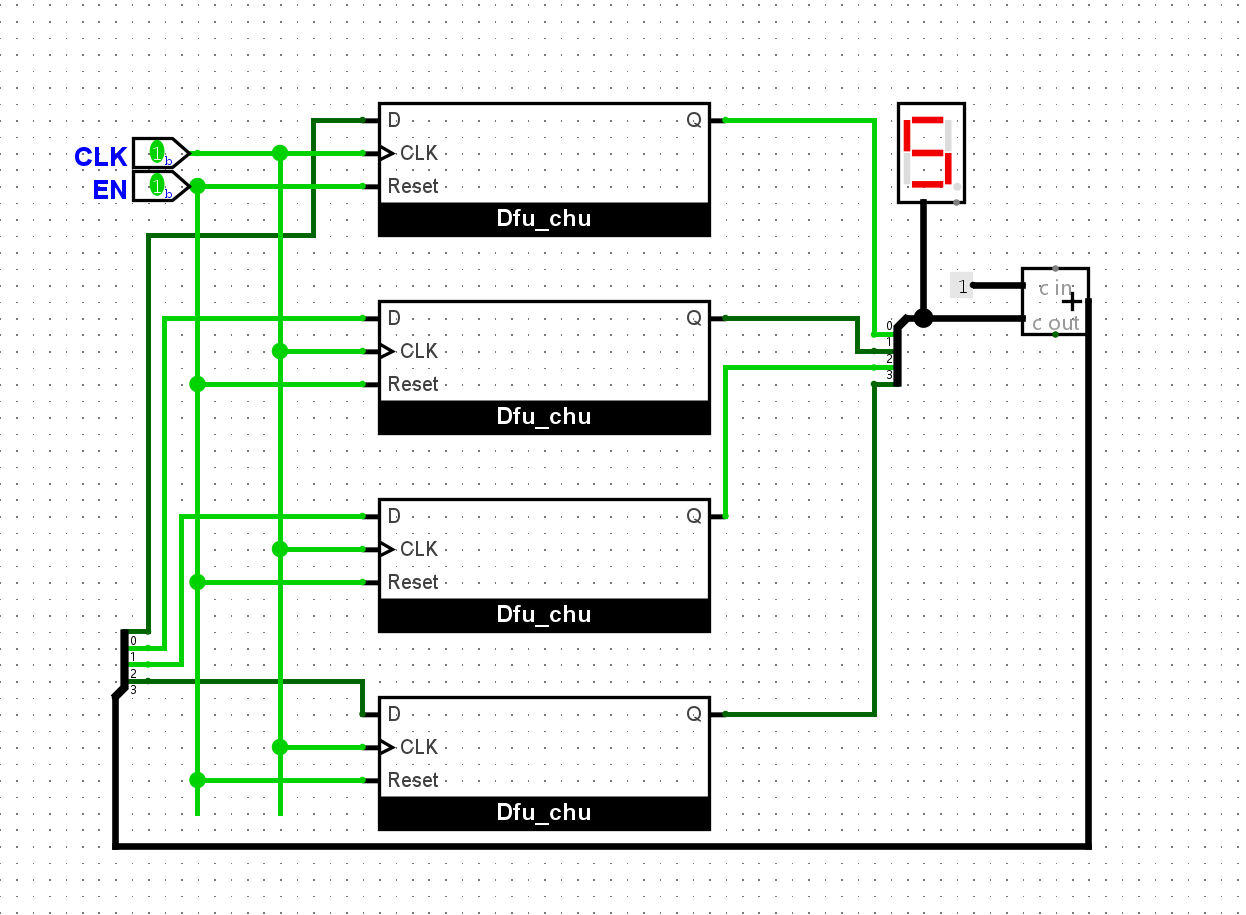

寄存器

上述的D触发器只能存储1位数据, 但有时候需要将多位数据作为一个整体来存储和处理. 寄存器(register)是由多个D触发器组成的存储元件, 其电路结构如下图所示. 这些D触发器之间共享相同的时钟信号和使能信号, 从而实现整体存储的效果.

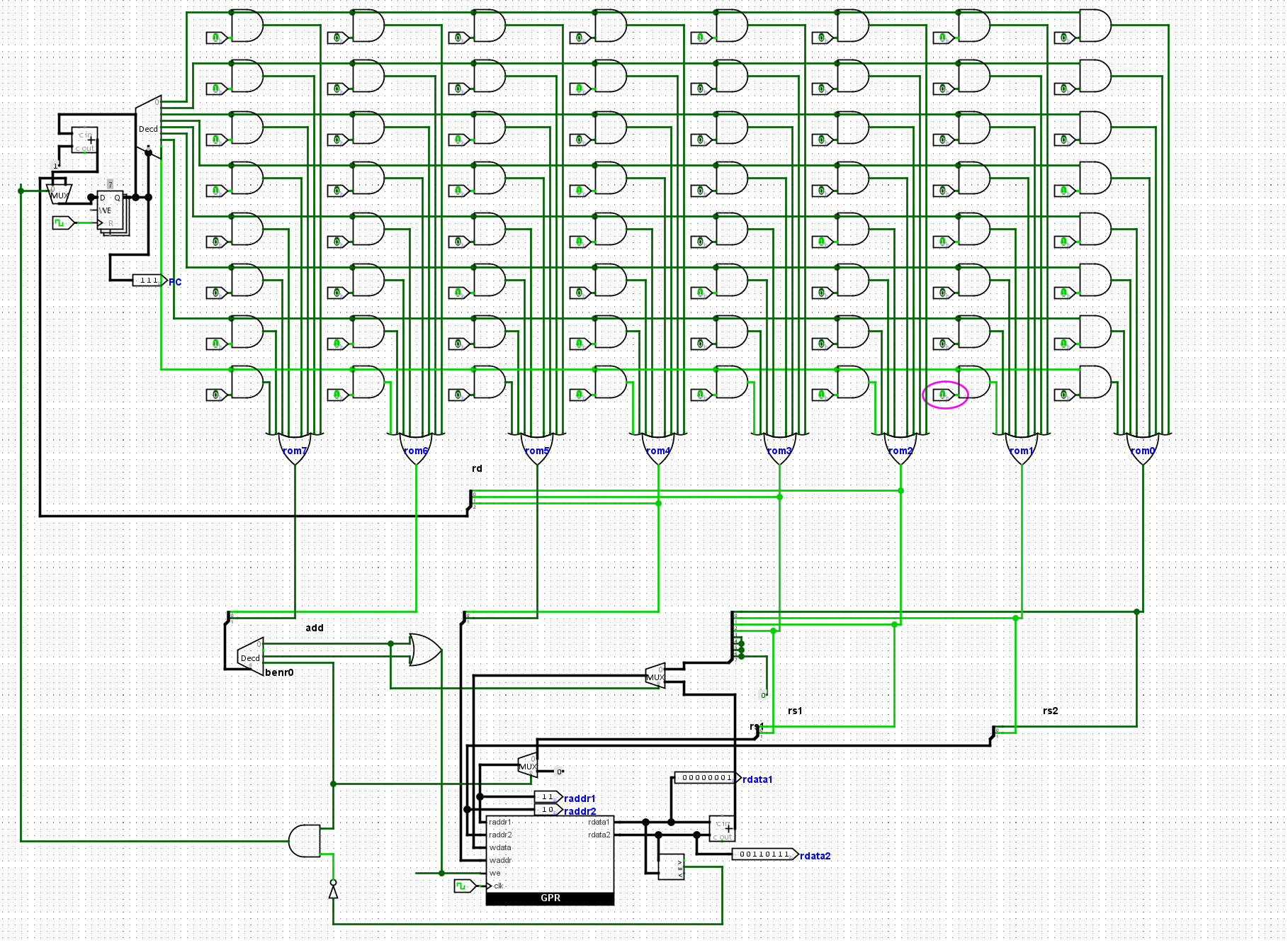

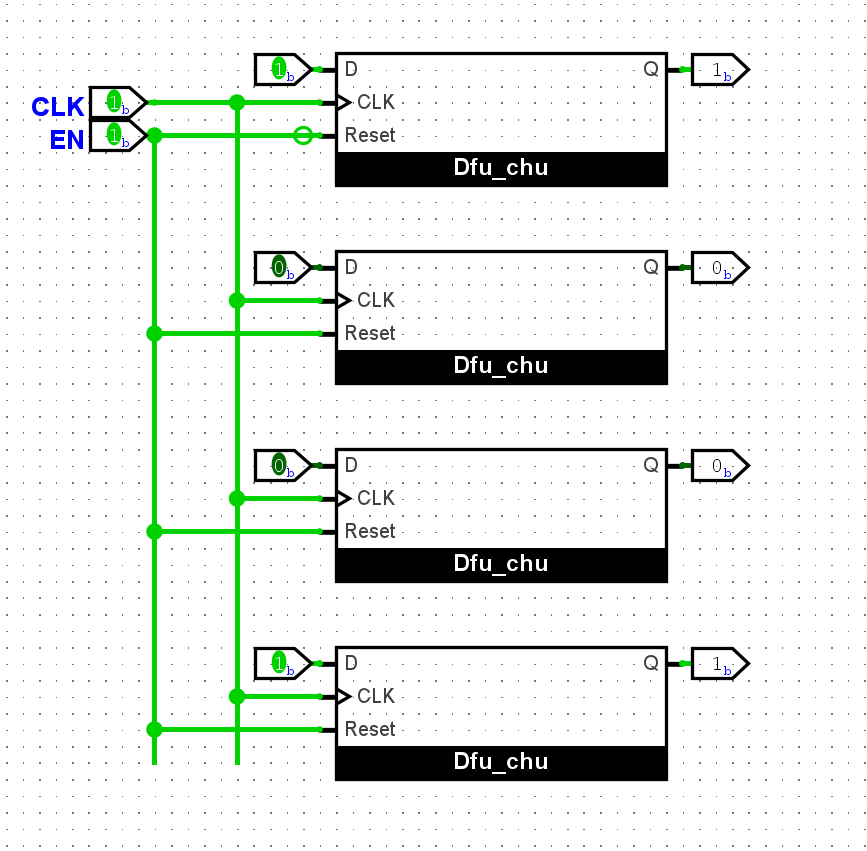

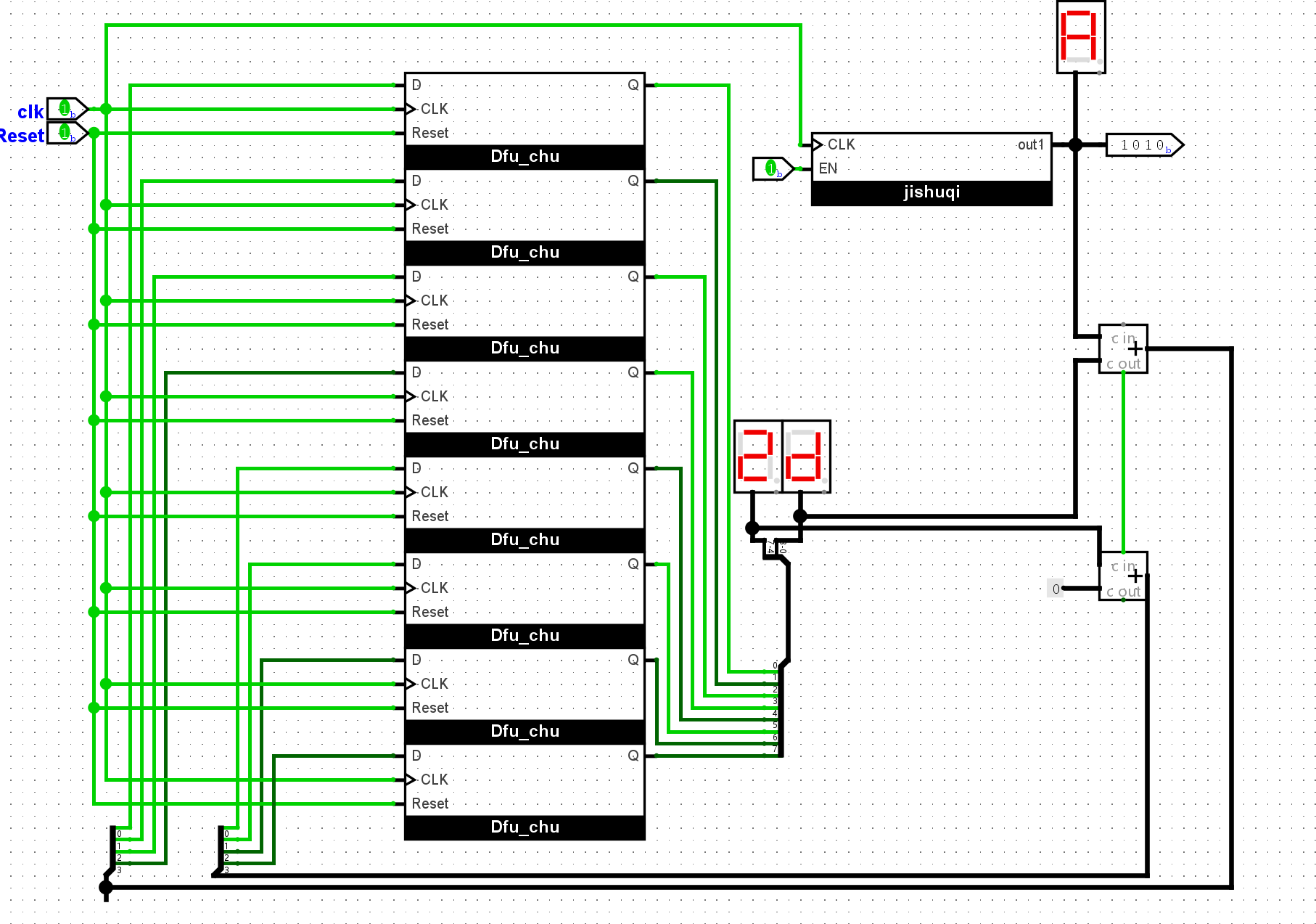

直接拿下!!手搓计数器,成功搭建4位计数器

设计数列求和电路

13+2 x 16=55,就是1到10的求和,我中了嘿嘿

电子时钟暂略,苦力活,嗯!先快进一部分