F3.2 数字逻辑电路基础

通过门电路搭建基本组合逻辑电路

有了门电路以后,我们就可以通过多个门电路的组合来搭建一些在数字电路中常用的模块了

译码器

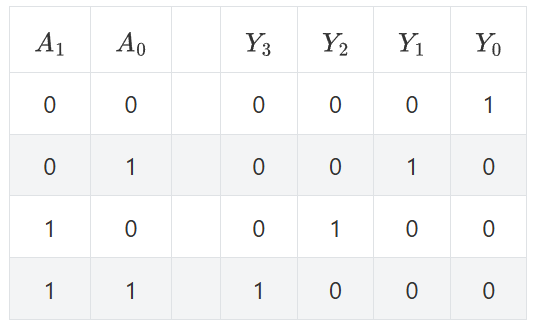

译码器(decoder)是一种将K位输入转换为最多2的K次方种不同输出的电路,一类常见的译码器是n选1译码器(1-of-n decoder),他将二进制输入解析为一个数值x,并且使得输入的第x位为1,其余全为0,也就是我们说的独热(one-hot)编码。其真值表和电路图如下:

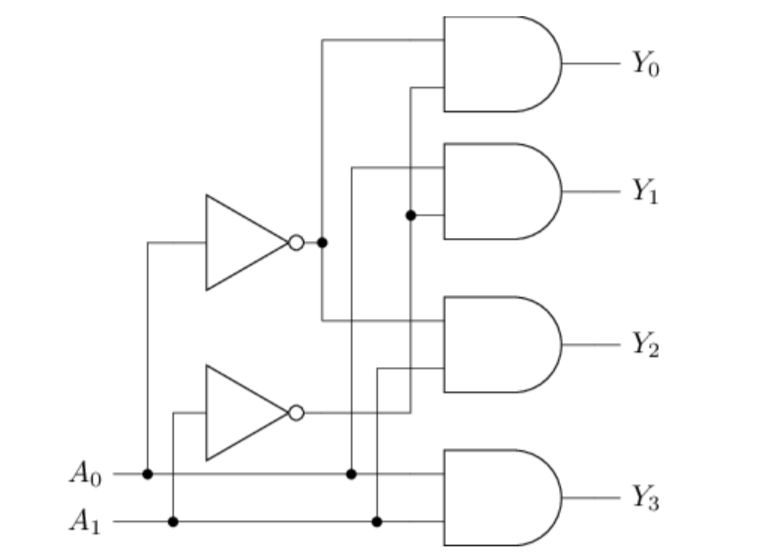

搭建2-4译码器

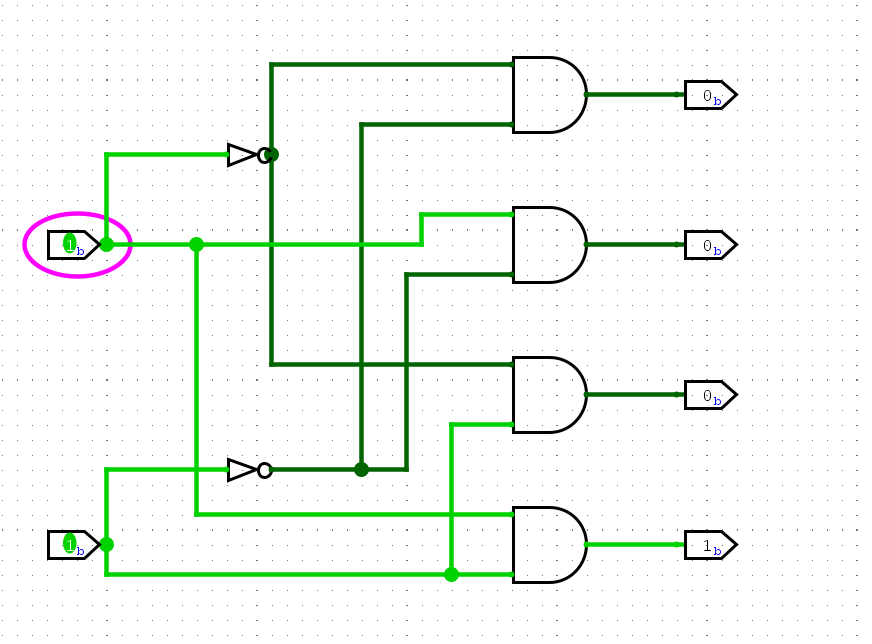

我们在logisim中进行实现,由于我们要进行编码,而输入为2,输出为4,我们需要将其两两进行逻辑运算。我们对于输入的两个信号进行非运算后,我们有了4个两两一组的元素可以进行比较。

由于其它都是0,只有一位是1,所以我们最终选择与门进行实现

在计算机中, n选1译码器常用于实现寻址的部分功能, 此时译码器的输入即为地址, 输出则是选择信号, 其中与地址对应的选择信号为1.

在现代计算机中,得益于存储单元之间的连续性, 如果计算机要访问其中一个存储单元, 它并不需要从第1个存储单元开始按顺序检查, 而是可以通过一个”行号”来快速找到对应的存储单元. 这个”行号”在计算机中称为”地址”, 根据地址找到相应存储单元的过程称为”寻址”。

计算机之所以能够通过地址快速找到对应的存储单元,本质上就是计算机可以通过N选1编码器将地址快速转换成为一组选择信号,后续通过这组选择信号选出目标数据。

子电路

译码器在后续的数字电路中的确时长用到,为了避免用户重复设计相同的电路,logisim提供了子电路功能,相应的电路只要设计一次,后续即可反复地进行实例化的过程

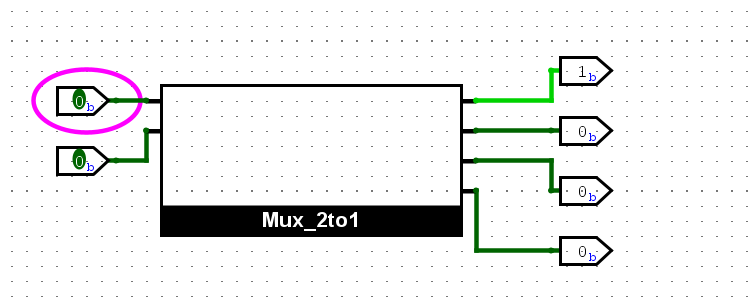

我们在项目中,点击“添加线路”然后命名,我们就可以打开新的窗口进行编辑,而后当我们回到main窗口中,我们发现我们即可拖用我们自己创建的封装,如图所示:

如上图所示,这是我自己绘制的子电路,忽略那并不那么正确的名字。

3-8译码器

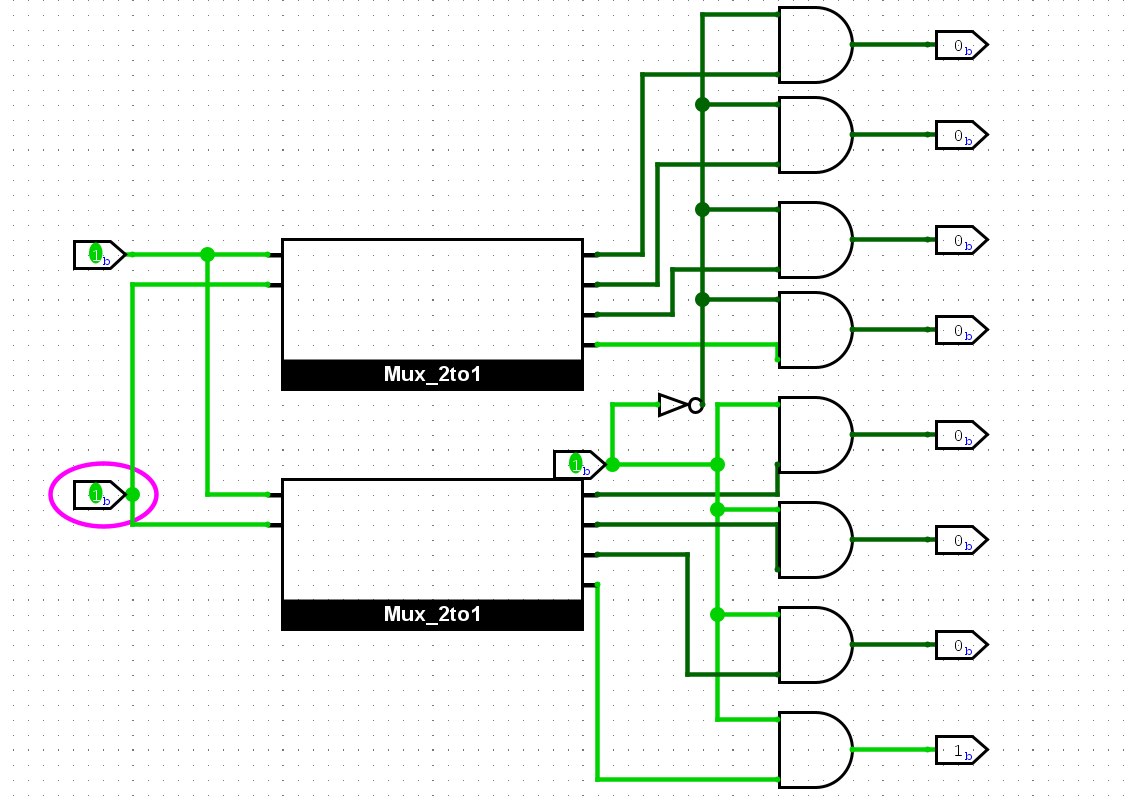

这似乎是一个很有趣的题目,我们需要借用这个2-4译码器的封装,自己去搭建一个3-8的译码器。

对于一个三位的译码器,我们可以采用如下的想法:

- 首先,先用两个2-4的译码器,分别输入电路的后两位,如输入是00,输出就是“10001000”从上至下

- 然后,我们在其输出端,分上下四个,分别使用与门,上端借信号,下端接其非信号

这是最后的成品的电路,虽然但是丑是丑了一点点

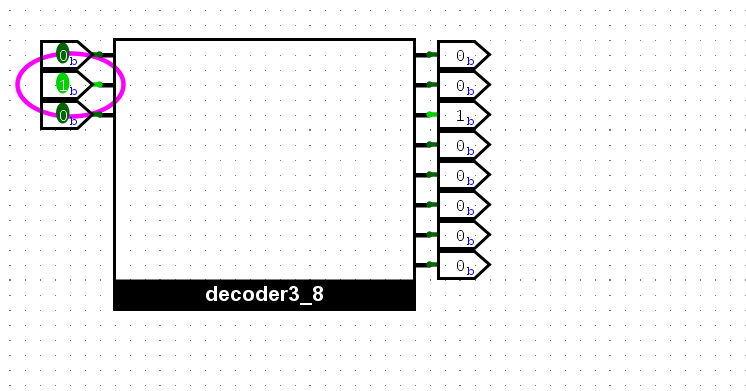

这是我完成封装以后的电路:

搭建七段数码管译码器

实际上应该叫做转码器

以下是来自“一生一芯”的官方文档的要求,我们复制如下:

尝试在Logisim中通过门电路搭建一个七段数码管译码器, 它有4位输入和8位输出, 分别与拨码开关和七段数码管相连. 七段数码管译码器支持十进制数字的显示, 即当输入对应0-9时, 七段数码管显示对应的数字; 对于其他输入, 七段数码管只显示小数点. 搭建后, 通过仿真检查你的实现是否正确.

Hint:

- 七段数码管元件可在元件库中找到, 实例化后, 可以通过将鼠标指针悬停在元件的端口上, 来查看该端口的功能描述.

- 可以先用n选1译码器生成一组独热码, 然后再通过一层或门来分别决定每个发光二极管在哪些输入的情况下应该点亮.

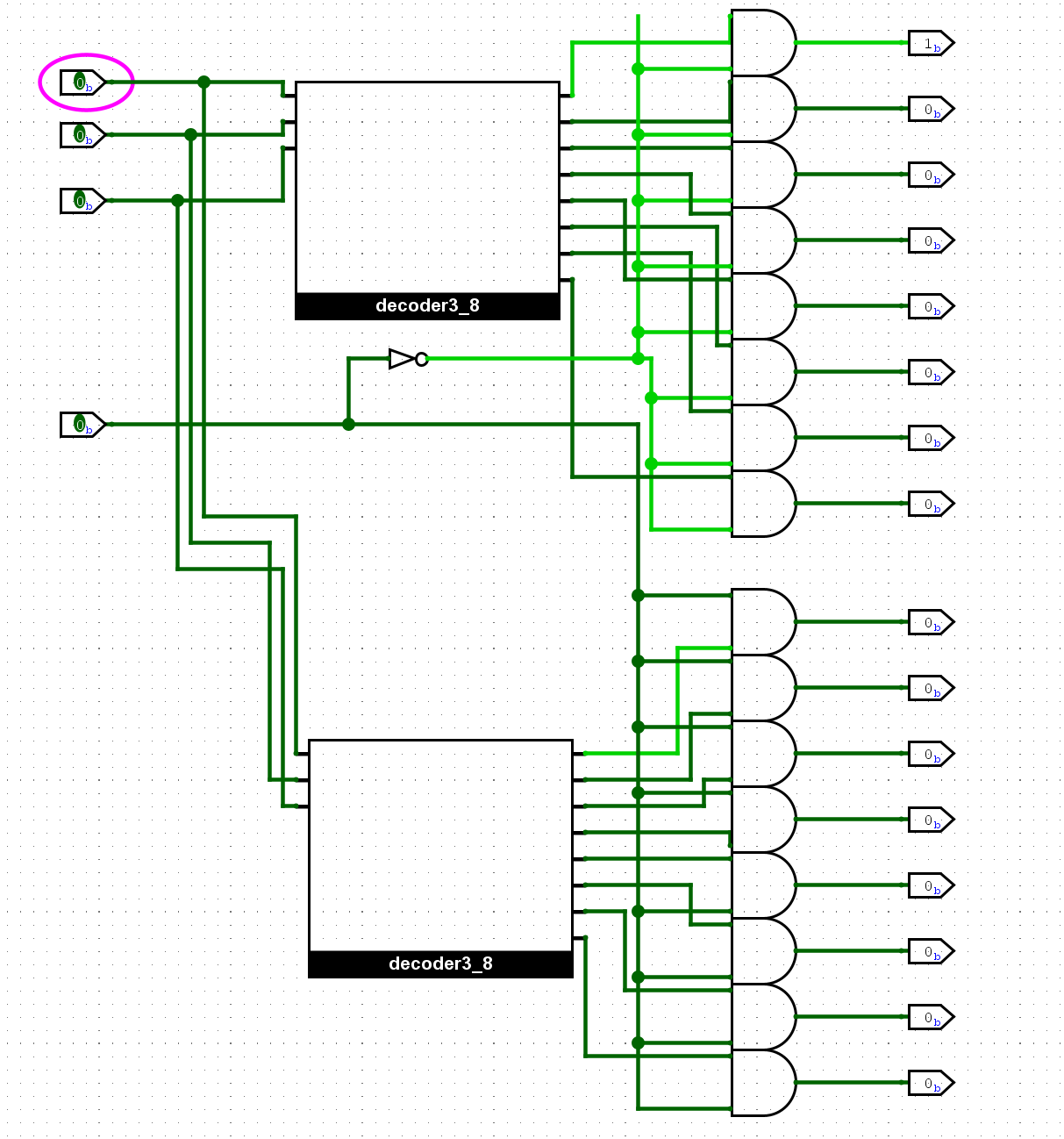

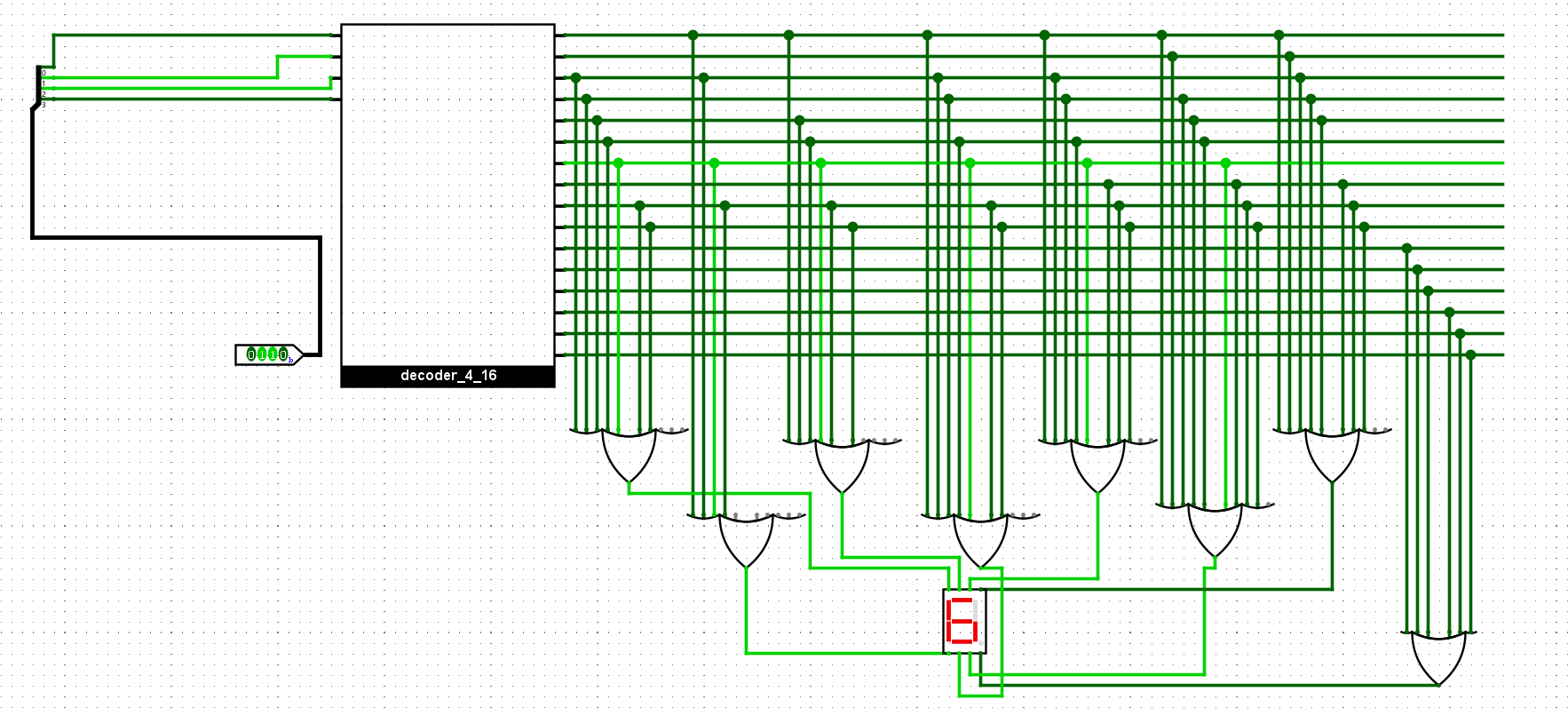

理所应当的,我们也选择使用4-16的decoder进行one-hot编码,然后生成最终的结果.我们首先,搭建了一个4-16的译码器

有着logisim一贯的风格。

很不错的是,搭完啦

尝试在Logisim中通过门电路搭建一个支持十六进制数字的七段数码管译码器. 和上述的十进制数字相比, 当输入对应10-15时, 七段数码管分别显示A, b, C, d, E, F. 搭建后, 通过仿真检查你的实现是否正确.

非常可恶的第二问,我们没有留下足够的空间,让我们的创作变得非常的困难,所以我们就略去这并不复杂的一个章节,next!!!

编码器

编码器的功能和N选1译码器的功能刚好相反,用于将独热码转换为对应的二进制数值,具体来说,编码器有2的N次方的输入,N位输出,如果输入不为独热码,则输出未定义

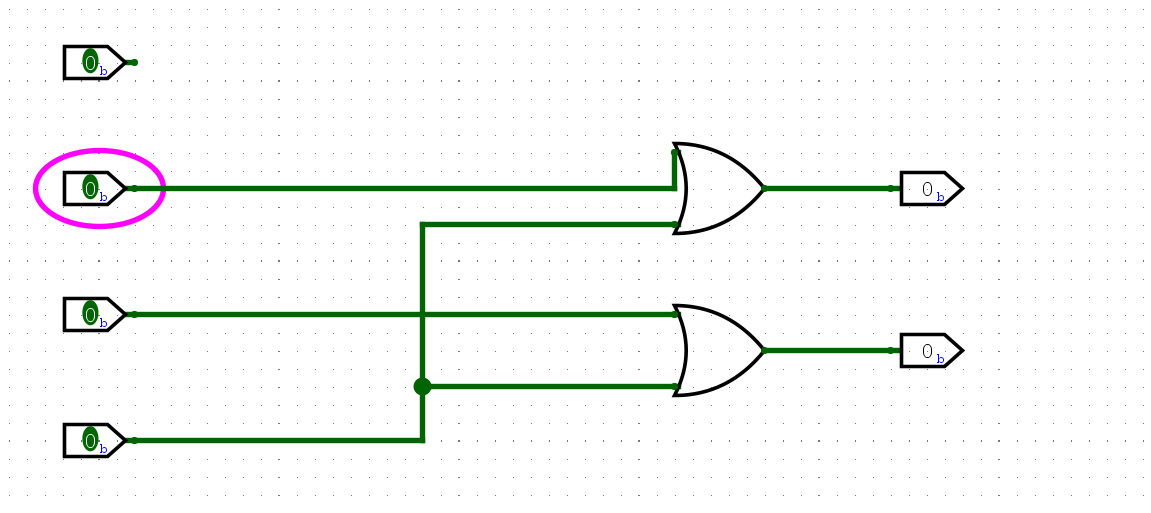

not defined是我们程序中非常难缠的一些报错,就好比“除数为0“的情况,我们来搭建编码器,分为简单的编码器和4-2的优先编码器,以下是编码器的一个简单的实现。

只不过,真的没有人觉得连连看很解压吗

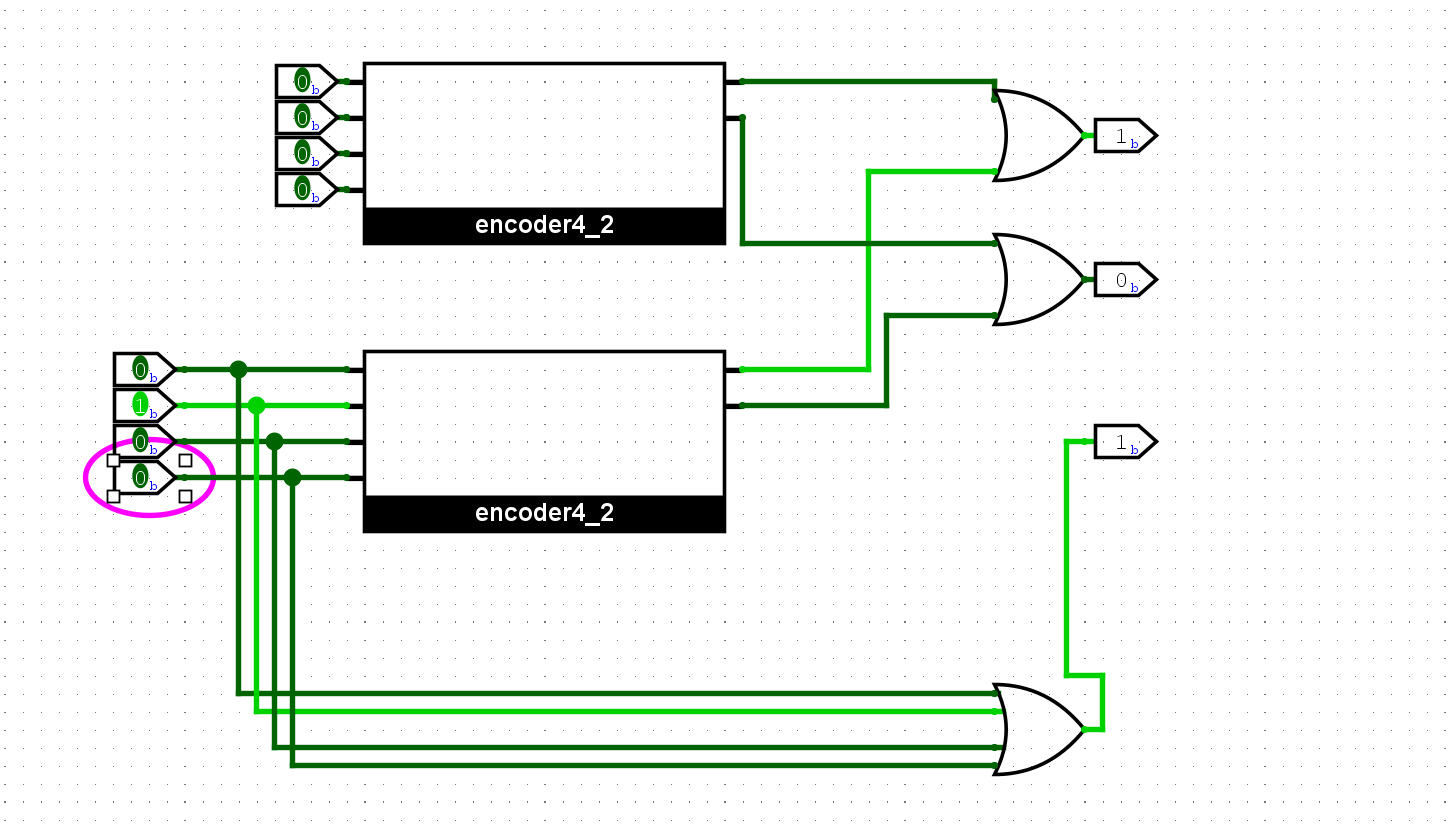

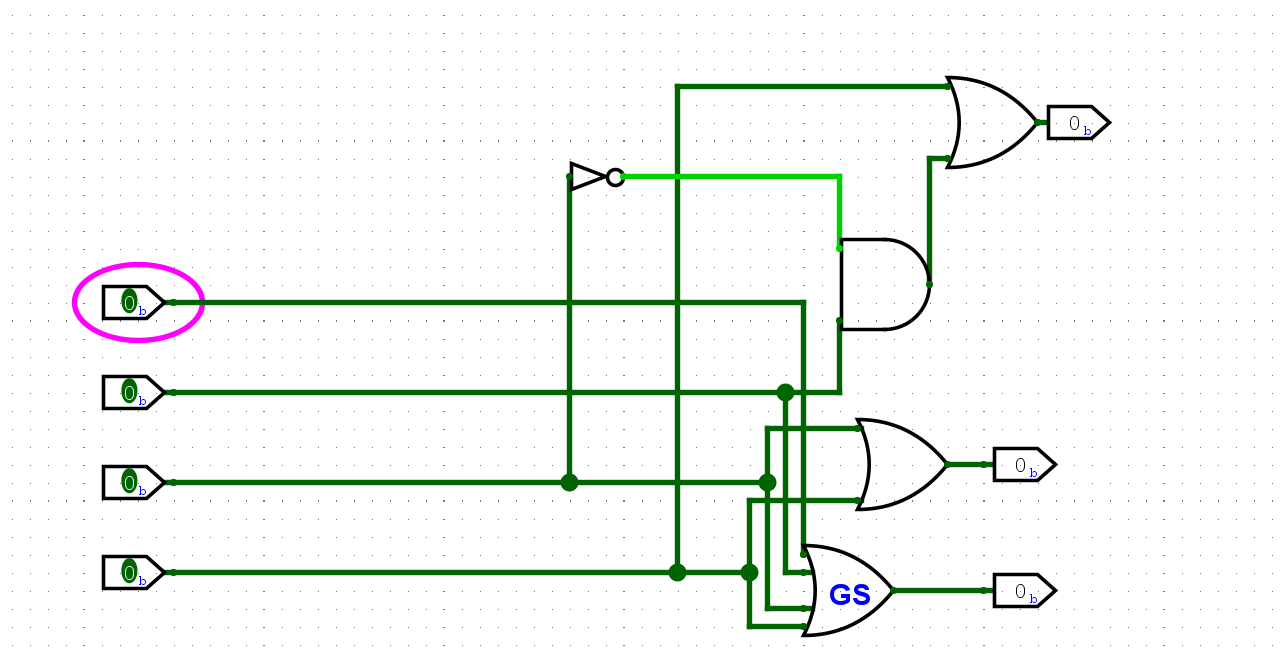

我们也是非常高效的完成了正经的编码器,接下来我们需要完成优先编码器,优先编码器我们只需要考虑有限个逻辑,该有限编码器的输入为X0X1X2X3输出为Y0Y1,以及一个信号用于表示是否是正确的输入。

普通编码器只需要两个OR门,而优先编码器支持多位输入,但需要2个OR门,1个NOT门和1个AND门。

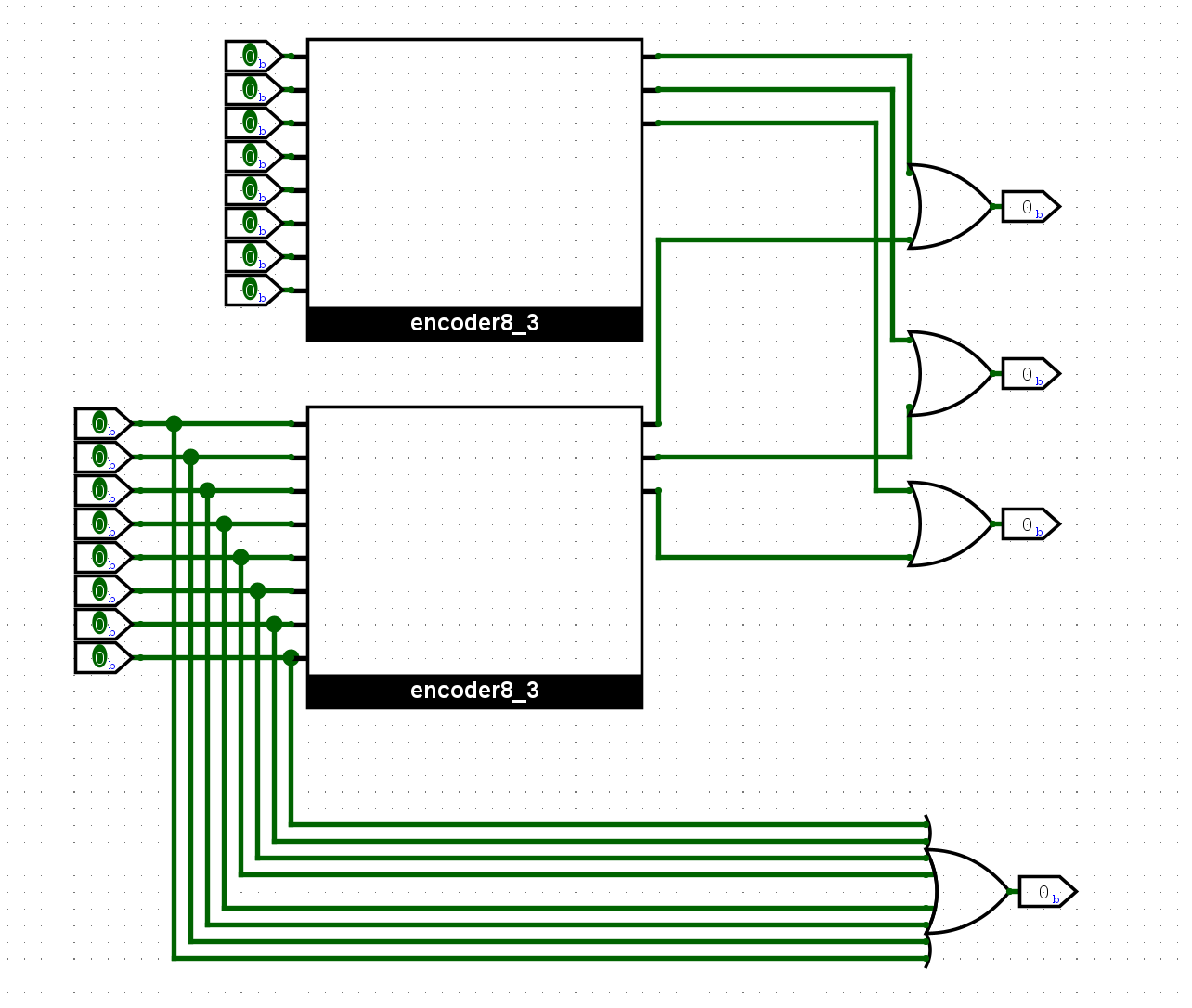

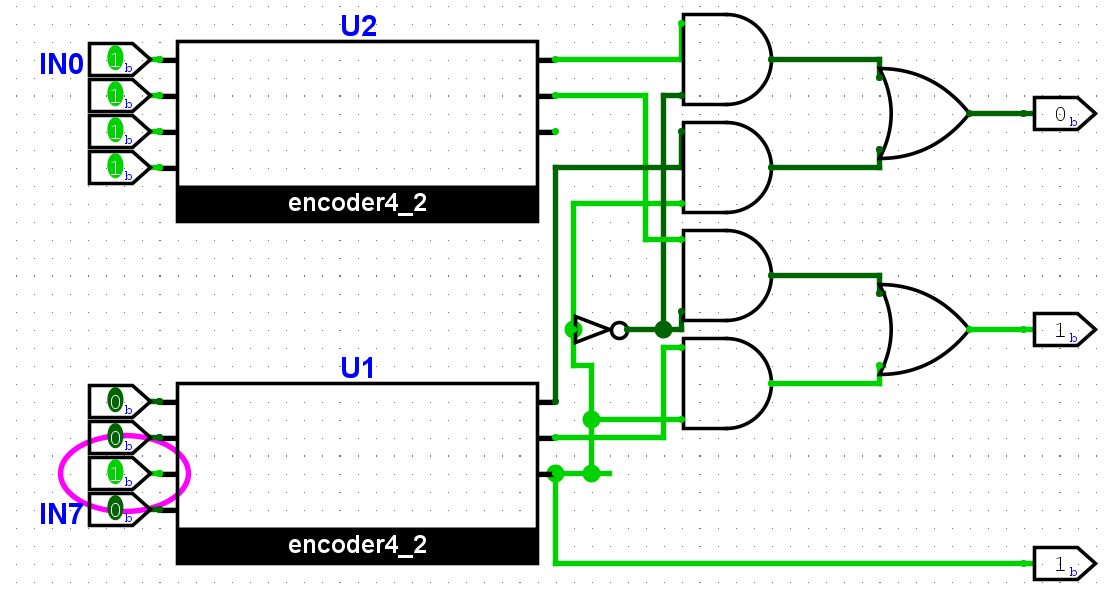

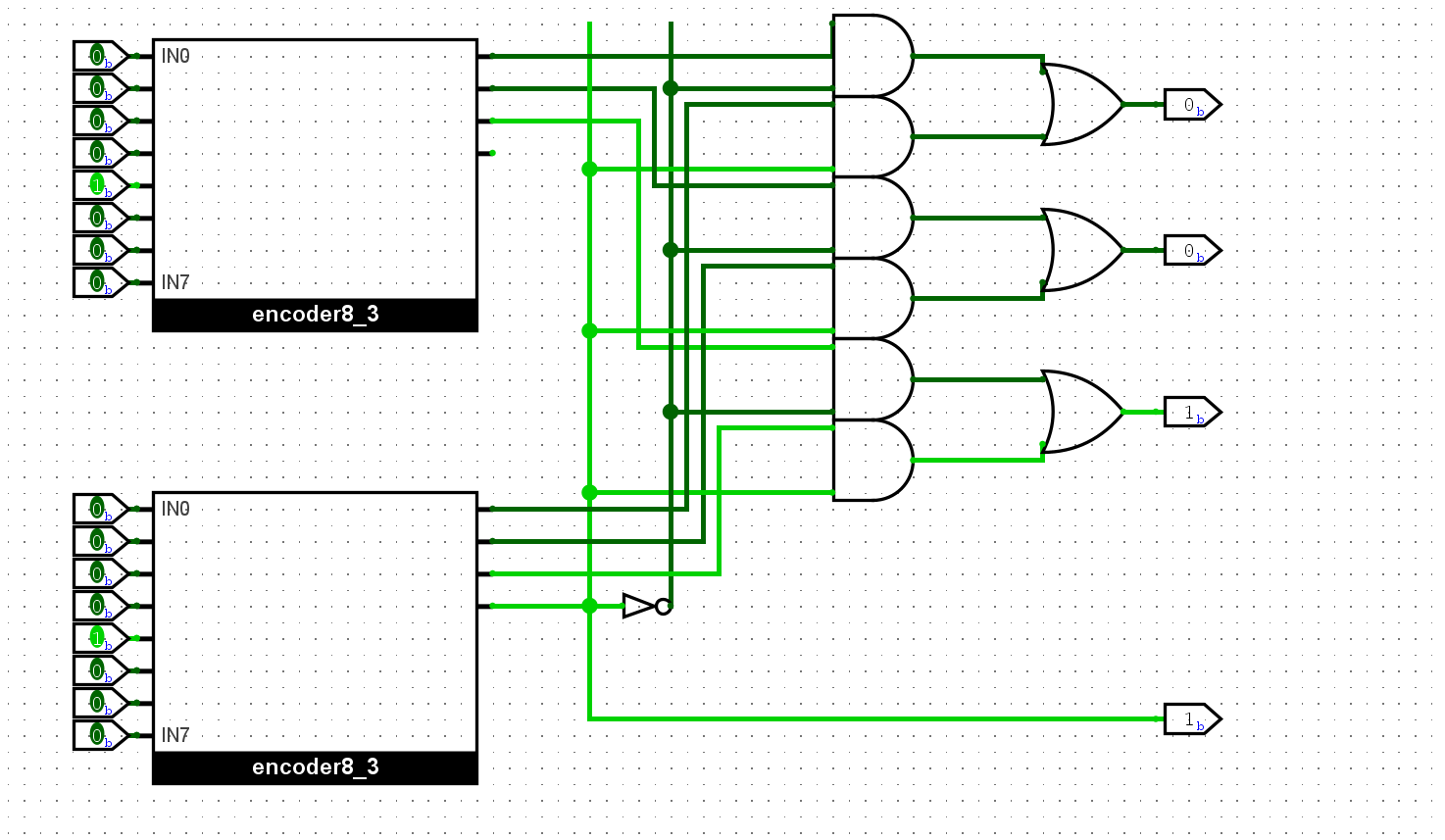

16-4的优先编码器

这是我们搭建的8-3的优先编码器,老规矩,我们还要预留一个代表着是否有输入的GS口

也是完成了,我觉得主要的思路其实是,输出=GS为真时一路的输出+GS为假使1路的输出,最终两个的输出取一个或门就有了最终的结果。如果对于一个长二进制的数,我们可以在正向和反向分别进行优先编码,从而可以知道数据的前导0和前导1的数量。

多路选择器

搭建一个3位4选1选择器,这个似乎真的不难,编码器+与门最后一个四路与非门就OK了,很简单的。

比较器

异或门秒了

加法器

有点意思这个加法器

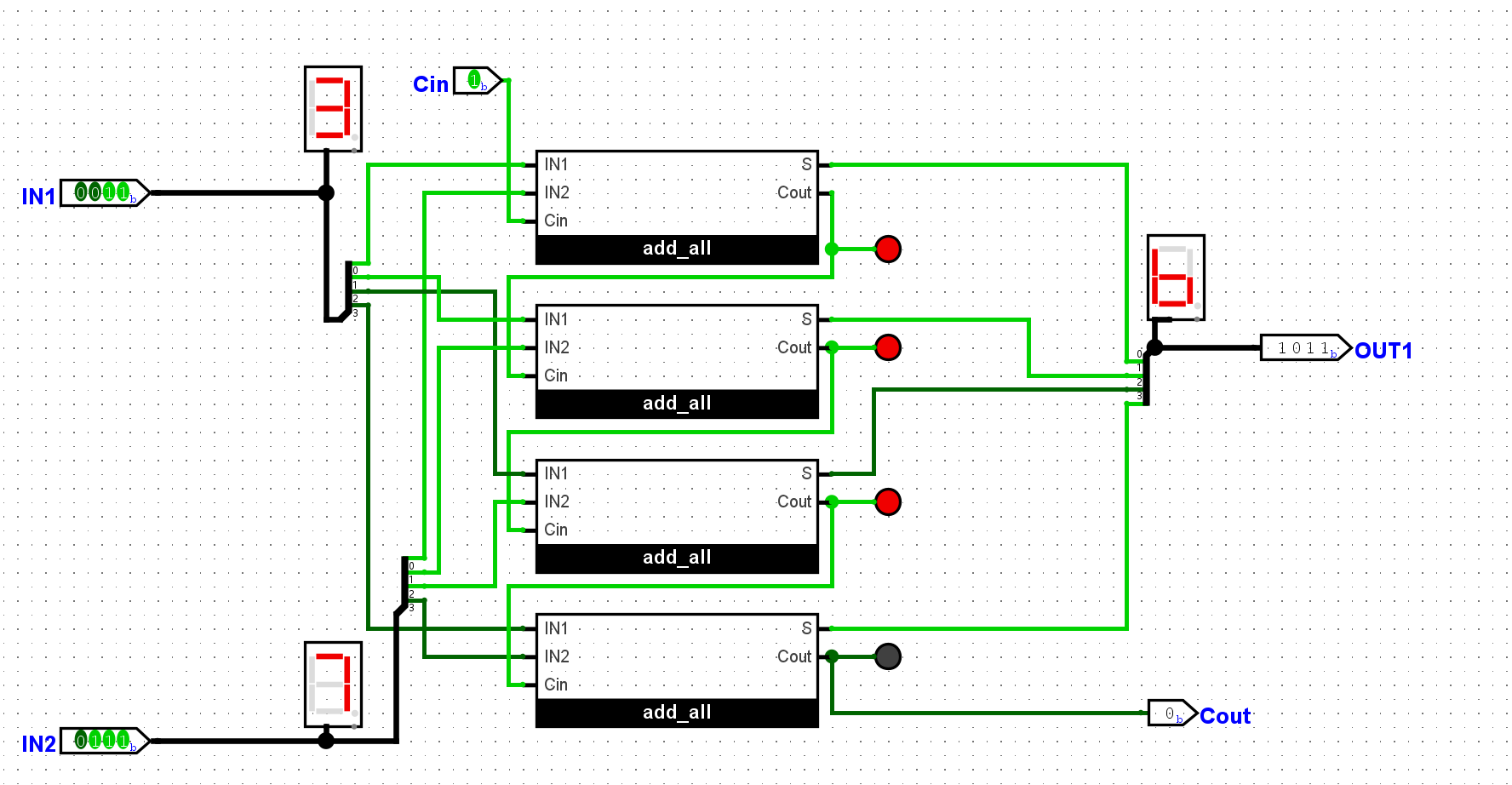

尝试在Logisim中通过门电路搭建一个4位加法器, 用七段数码管按十六进制显示加法器的两个输入和结果, 并用一个LED灯指示加法结果是否产生进位. 搭建后, 通过仿真检查你的方案是否正确

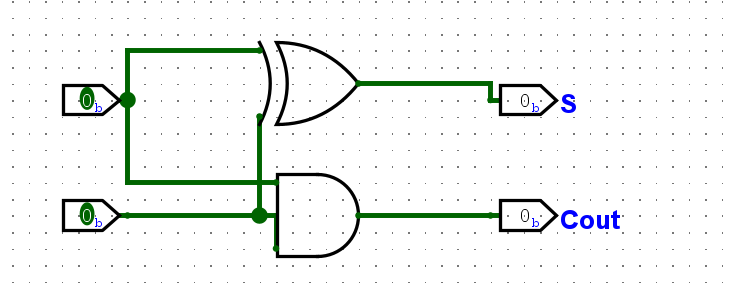

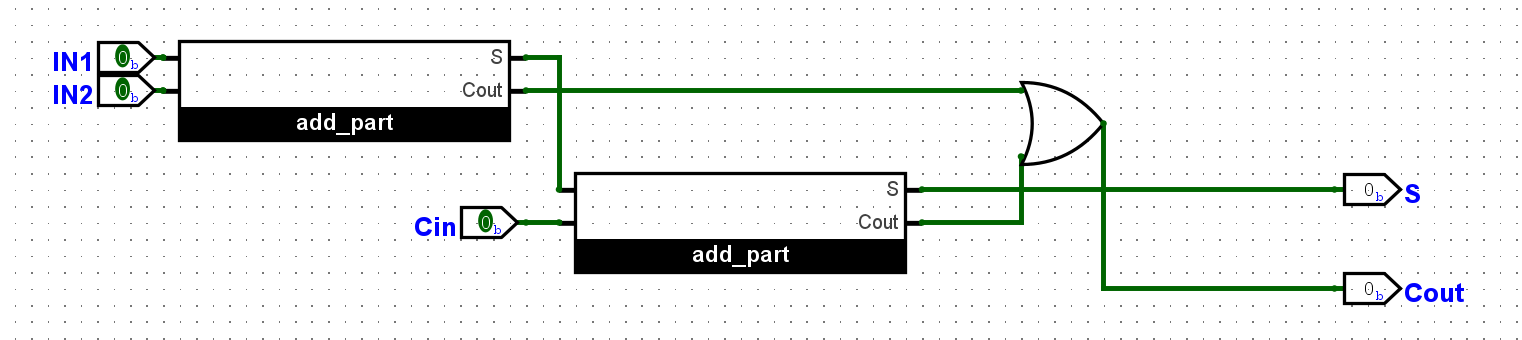

这是一个简易的一位的半加器的实现,接下来我们要实现的是全加器

这是一个三位输入的全加器。接下来的任务是搭建一个现实可用的全加器

尝试在Logisim中通过门电路搭建一个4位加法器, 用七段数码管按十六进制显示加法器的两个输入和结果, 并用一个LED灯指示加法结果是否产生进位. 搭建后, 通过仿真检查你的方案是否正确.

看样子还是非常成功的