F3.1 数字逻辑电路基础

这是“一生一芯”项目的一个beginning,千里之行始于足下,希望能够通过自己的学习和体会,在下个学期末之前完成流片。如果我的数电的大作业最后是自己搭的一个芯片,我真的觉得那样酷毙了,learn for fun。

处理器本质上是数字电路,而数字电路是用来处理数字信号的电路,而数字信号简单来说就是指0和1这样两种练得信号。0和1并不是数字意义的自然数的前两位,而是电路的高电平和低电平的两种不同的状态,所以有的时候也会把它们称之为逻辑0和逻辑1。

模拟信号是连续的,像是电流和电压一样。

想要学习数字电路,学习处理器的芯片设计,数字电路的知识是基础,而要学习数字电路,就是要学习信息在数字电路中是如何表示,处理和存储的。

通过晶体管实现0和1

0和1是抽象的,在数字电路中,0和1一般来说依靠晶体管进行实现,我们常常采用MOSFET(金属-氧化物-半导体场效应晶体管),根据用途的不同,一般又分为nMOS ,和pMOS,管两种。在模电中,我们一般运用的是场效应管的放大效应,即其对电压的放大能力,而在数电中,我们一般使用其开关特性。原理不进行赘述,参考模电教材。

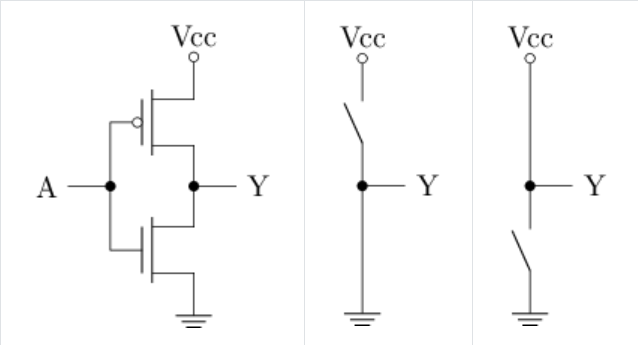

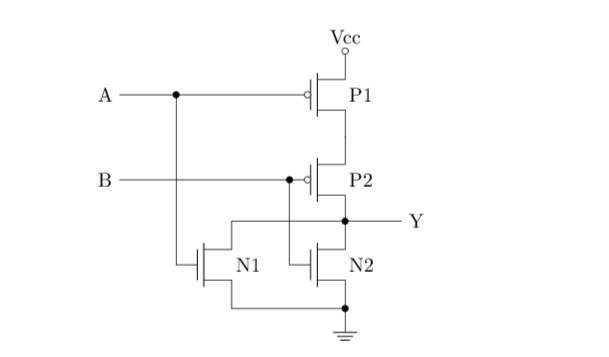

接下来我们学习CMOS(Complementary Metal-Oxide-Semiconductor)技术。由于nMOS和pMOS具有互补的特性, 在数字电路中通常将两者联合使用。下面是一个最简单的CMOS电路:

这里采用的是增强型的MOS管,即当电压为0时,并不存在导电沟道,我们分两种情况进行分析。

- A加高电压时,下方的MOS管导通,而上方的MOS管截止,所以Y点与地相连,输出低电平

- A加低电压时,上方的MOS管导通,而下方的MOS管截止,所以Y点与Vcc相连,输出高电平

这两种状态就是数字逻辑电路的两种基本状态

通过晶体管搭建门电路

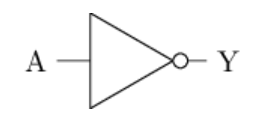

非门

unbelievable!!!

相信聪明的你不难发现,上面的那一张图片,竟然是一个彻彻底底的非门电路!!!

高电压时输入低电平,简直fancy!!

这个门电路就是非门,也叫做反相器。图表是一个三角形加一个圆圈,在门电路的语言中,小圆圈就代表着取反。

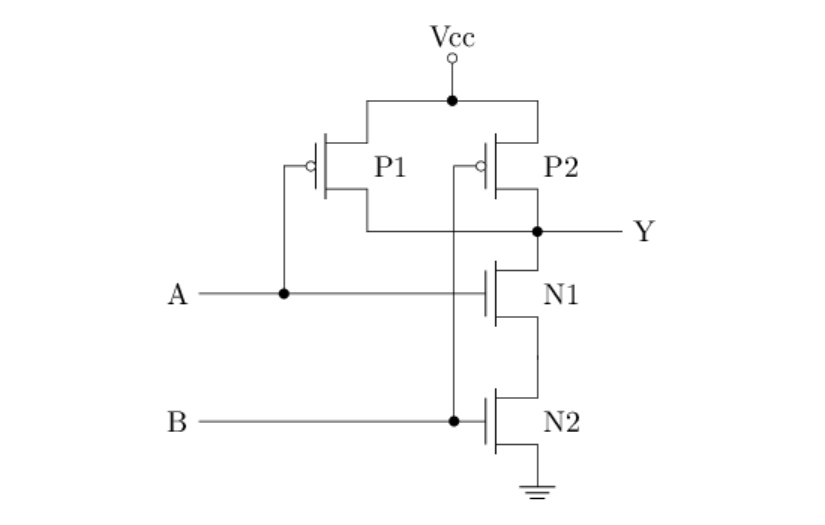

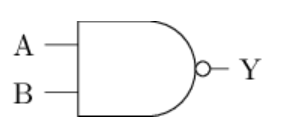

与非门

之前的模电的大实验的时候,所使用的74HC00N芯片也是一种14脚与非门器件。一句话概括这个器件就是1和1生成0,其它都是1.

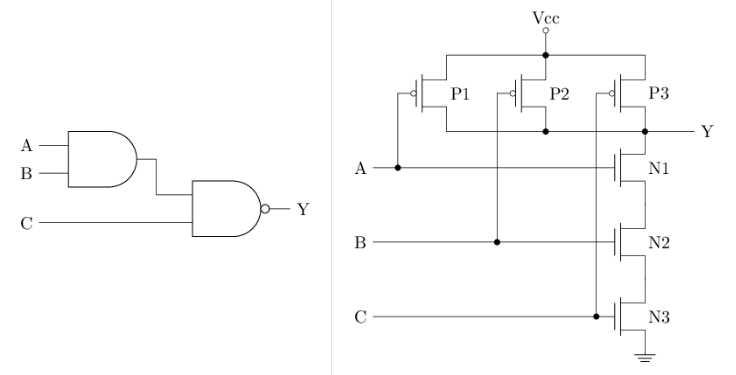

这是一个与非门的电路,我们对它进行分析。

N1N2是串联架构,而P1P2是并联架构,所以:

- 如果A和B都是高电平,N1N2导通与地相连,P1P2断开,最终输出为低电平。

- 如果A和B不全是高电平,N1N2至少有一个断开,即N1N2整体断开,但P1P2至少有一个会导通,所以输出为高电平。

不得不佩服,这一种想法非常牛逼,完美的将开关和串并连结构结合在了一起,非常天才的构思。

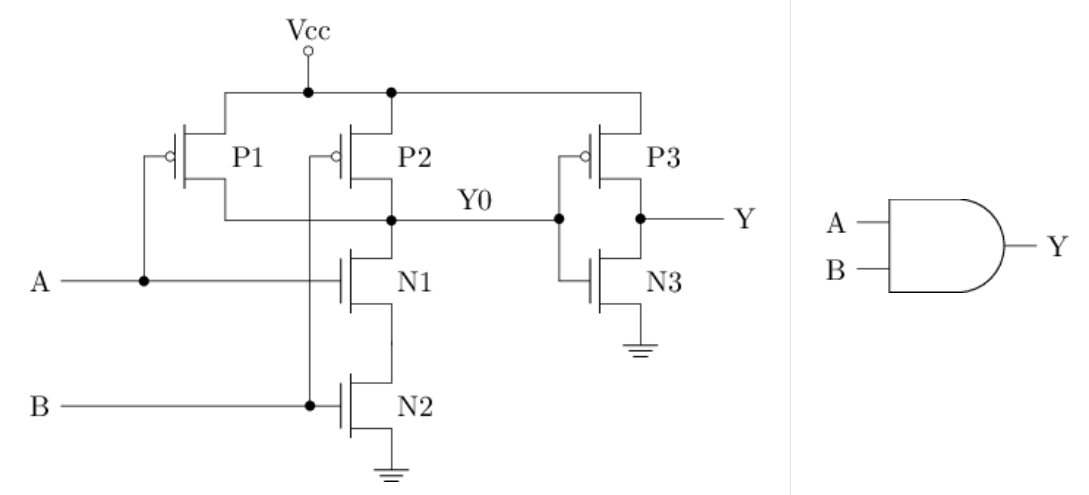

与门

有了上述的分析,与门实际上非常简单,就是在与非门上加了一个非门,其结构图和符号表示如下所示,与门的符号就是一个与非门去掉了一个圆圈,实际上是加上了一个非门。

Q&A

1.尝试分析一下门电路的行为和功能

- 当A,B均为0时,P1P2导通,N1N2不通,输出为1

- 当至少有一个是1时,P1P2整体不导通,N1N2至少有一个导通,输出为0

这个门电路的结构,依然是与非门

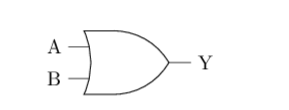

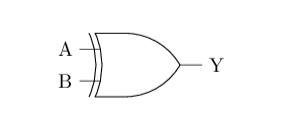

2.以下是或门的逻辑符号,尝试画出或门的晶体管结构

很大程度上是上面的那一张图,将VCC与GND的位置交换一下,即:

- pMOS端,并联

- nMOS端,串联

而后再经过一个非门,就得到了或门,思路仍然是参照上一部分

三输入与非门

我觉得这一个门电路的思路,可能比逻辑表示更好理解,其中只有当ABC三者全部为1时,输入为0,和两输入的与非门几乎是一模一样

异或门

用于计算异或(XOR),通常在处理逻辑数据时进行运用,其逻辑符号如图:

二者不同时,结果为1,否则为0。

同或门即为在此基础上进行一次取反。

“一生一芯”的小巧思

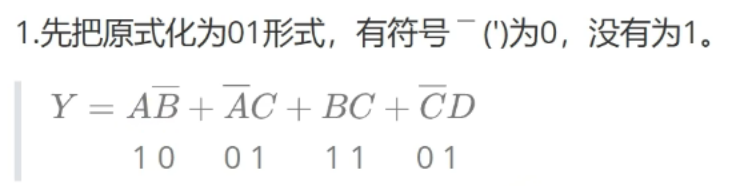

卡诺图化简

属实应该是数字电路的教科书上的必备的一个技术,我们将会因为考试而进行学习,显然的,我们需要在考试中用到,但在“一生一芯”这样的动手实践的项目上,显然是仅存在于理论的一个糟粕。

因为这个技术的课延展性的可扩展性非常的低,在真实的项目中,我们面对的变量和数量大概是五个及其以上的,要用卡诺图进行这样一个东西的化简,效率相比是非常低的。事实上,现代工具通常会采用QMC算法,或者espresso算法对逻辑表达式进行化简。

emm,好像乍一看根本看不懂这两个算法,还是等待上完数电后的自己

In all,还是很有必要对于这一个方法具有一定的了解,我也希望能够,在接下来的数电课程中,少学一点,多做一点。

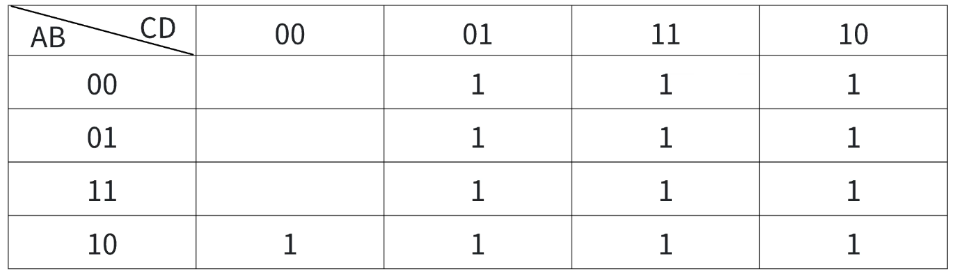

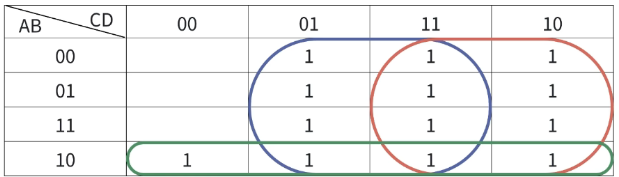

注意,卡诺图的顺序一定要是00,01,11,10

以BC项为例,即为将纵轴01,11和横轴11,10对应的2x2方格进行标注,经过以上的操作,我们得到了如上图所示的卡诺图。

然后进行画圈,有如下的要求:

- 圈的数量少、范围大

- 圈可重复圈,但每个圈必须要有新的最小项

- 每个圈包含的小方格数量必须是2的N次方项,如1 2 4 8

- 看绿圈,CD的值都进行了变化,而AB的值保留为10不变

- 看蓝圈,AB的值都发生了改变,而C发生了改变,D没有变

- 看红圈,AB的值都发生了改变,而D发生了改变,C没有变

感觉卡诺图还是比较有意思的捏

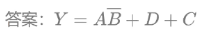

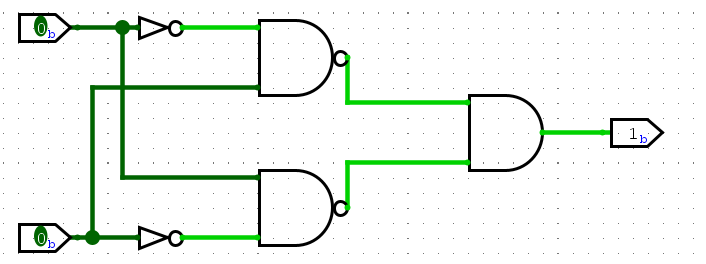

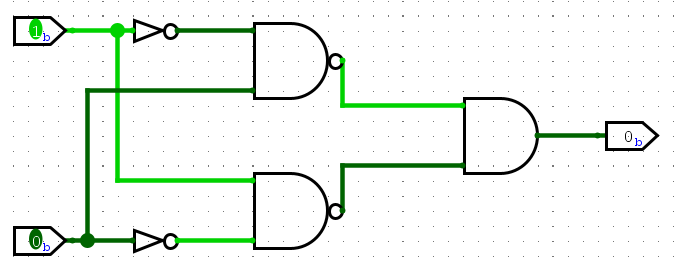

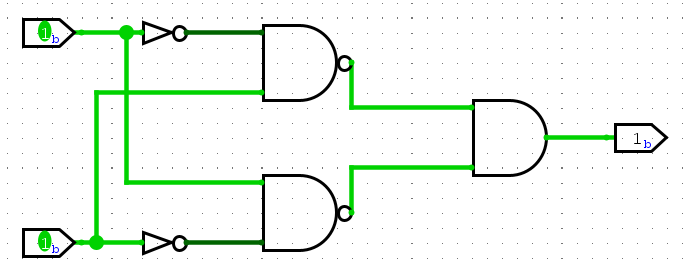

搭建异或门

异或门的确是相当的神奇的一个电路,我们尝试使用其它的门电路去实现它,然后用过仿真检验是否正确,并且计算我的方案使用了多少个晶体管。

对于11和00而言,最后要进行0和0的运算得到0,而对于01和10而言,最后要通过1和0得到1,显然,这种逻辑关系,我们可以用或门进行实现。所以我们最后的设计电路需要:

- 两个与非门

- 一个或门

与非门需要四个晶体管,而或门需要六个,amazing!刚好十四个

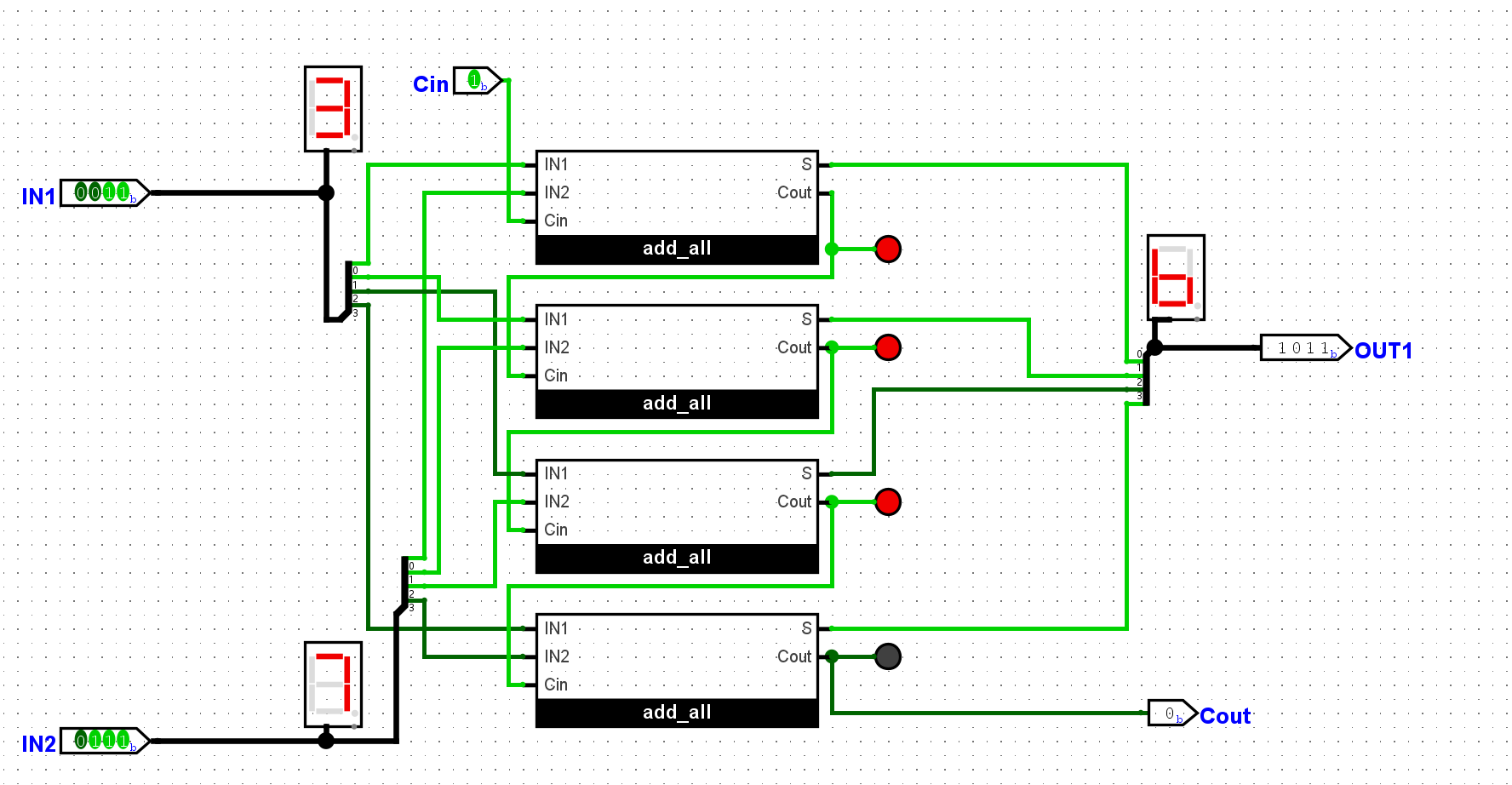

但好像搞错了,我的logisim如下

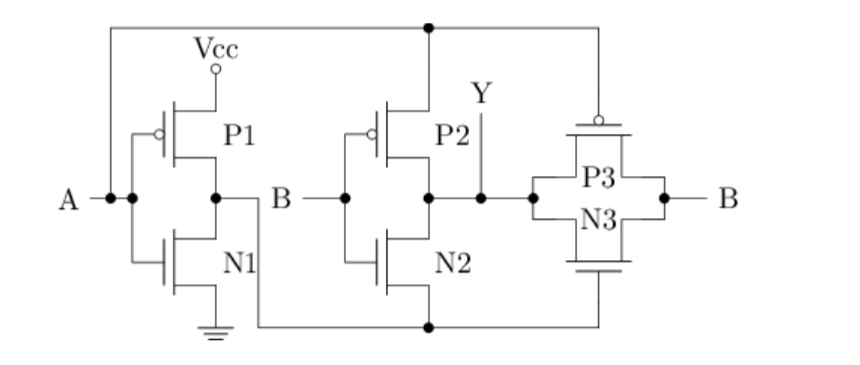

异或门的全定制电路:

真真切切的体会到了,什么是0帧开大,这是我能学会的吗。

这和真值表和逻辑的表示是紧密的相关的,通过我们真值表,我们不难看出异或门可以表示为

- 当A=0时,输出B

- 当A=1时,输出非B

最左边的操作是用来生成非A信号,而另外两个,则是相反的传输门。 - 对于传输门1,P2N2进行分析,如果按照原始的上源下地而言,这个结构是一个基本的反相器,但由于其上源下地的控制电压是由A和非A决定的,所以我们可以分析:A为1时,传输门1对A取反,A为0时,上地下源不满足要求,故不会导通。

- 但感觉AI说的这个传输门1,似乎更像一个带控制的非门。

- 传输门2是一个正经的传输门,当控制信号A取0时,上方的控制信号是0,而下方的控制信号是1,上下导通,相反则截止,类似与一个开关。

美妙

同或门

听说最小可以只用6个,真的可以这么恐怖吗。

相比有了上述的那个震惊的结构,这个真的只是去洒洒水啦,只是把刚刚的异或门的全定制电路的A控制信号,正反的控制极性反一下,在A为0时输出非B,在A为1时输出B,就OK啦

进位计数法

我们已经知道,cMOS电路可以用来表示和处理0和1的信号,但我们的物理世界并不只有0和1,因此需要考虑如何用1和0来表示物理世界的各种信息,我们把这样一种表示方法称之为编码(encoding)。二进制和十六进制法,在python的数据结构中我们大概已经有了体会,实际上并不难。我们在这里略去。

参考:

1.卡诺图相关:【卡诺图化简详解】https://www.bilibili.com/video/BV1P7ZYY9EDX?vd_source=0bcaeb0bf7fa61601fea861152f447e7